# 平成26年度 ものづくり中小企業・小規模事業者等連携事業創造促進事業 (戦略的基盤技術高度化支援事業)

# 「多チャンネル信号入出力と信号再現を可能とする マルチ・ハイスピードデータロガーの開発」

成果報告書

平成 27 年 3 月

委託者 中 国 経 済 産 業 局

委託先 公益財団法人ひろしま産業振興機構

# 目 次

| 第 | 1 章   | 章 研究開発の概要                                        |    |

|---|-------|--------------------------------------------------|----|

|   | 1-1   | 研究開発の背景・研究目的及び目標                                 | 1  |

|   | 1-2   | 研究体制                                             | 5  |

|   |       | (研究組織・管理体制, 研究者氏名, 協力者)                          |    |

|   | 1-3   | 成果概要・・・・・・                                       | ç  |

|   | 1-4   | 当該研究開発の連絡窓口                                      | 10 |

|   |       |                                                  |    |

| 第 | 2章    | 章 本論                                             |    |

|   | 1 テ   | ータ圧縮と並列制御システムの高速化手法の開発                           | 11 |

| 2 | 2 多   | ・チャンネル大容量データのリアルタイム記憶・再生手法の開発                    | 16 |

| ; | 3 製   | !品化に向けた実装技術 ···································· | 19 |

| ; | 3-①   | マルチ・ハイスピードデータロガーの組立・調整                           | 19 |

| : | 3-(2) | 新たな電子機器としての要求性能の確立                               | 27 |

3-③ モデルベース開発ツールとしての有効性の確立 …… 30

### 第1章 研究開発の概要

# 1-1 研究開発の背景・研究目的及び目標

#### (1) 研究開発の背景・目的

品質制御、開発工程管理、開発コスト管理に係る技術の高度化において、カーエレクトロニクスの高度化に伴い、各種センサを活用した新しい電子制御ユニットの高知能化が進展している。自動車の過酷な環境下で長時間使用可能な高信頼性確保と低コスト化、及び新しい制御システムの高度化・複雑化に対応する自動車の電子制御ユニット(ECU)開発の最適化に応える為に、「多チャンネル信号入出力と信号再現を可能とするマルチ・ハイスピードデータロガーの開発」を行う。

従来のデータロガーでは、サンプリング速度 100MByte/sec で 64 チャンネルが限界であった。これに対し、本研究では、最大 128 チャンネルから送り込まれる 400MByte/sec のデータを SSD などの記憶装置にリアルタイムで蓄積する。また、各測定ポイントのデータの同期を保証すると共に、従来のデータロガーには存在しない「記憶データをアナログ信号出力として再現(リプレイ)する新しい機能」を備えたマルチ・ハイスピードデータロガー(計測装置)を開発し、ECU 開発の速度向上(期間短縮)を図る。

#### (2) 研究の概要及び開発目標

カーエレクトロニクスの高度化に伴い、各種センサを活用した新しい電子制御ユニット (ECU) の高知能化が進展している。言い換えれば、「車載する高品質な電子制御ユニットを 如何に短期間で、効率的かつ正確に開発するか」が自動車メーカにとって喫緊の課題である。

この顧客ニーズに応えるべく、本研究は、「従来の性能を凌駕する複数のセンサ信号を高速かつ精密に処理する能力と、記憶したセンサ信号をアナログ出力として再現(リプレイ)する新しい機能を備えた革新的なマルチ・ハイスピードデータロガー、を低価格で実現すること」を目的として、以下の研究開発により解決を図る。

### <目標値>本研究開発期間で得られる最終目標は次のとおりとする。

| 開発テーマ       | 目標値                                     |

|-------------|-----------------------------------------|

| ①データ圧縮と並列制御 | データ圧縮と OS のオーバヘッド軽減、並列制御プログラム           |

| システムの高速化手法の | の最適化で, <u>目標速度 400Mbyte/sec</u> 。       |

| 開発          |                                         |

| ②多チャンネル大容量  | ファイルシステムのデータ転送量拡大方式(RAID0:スト            |

| データのリアルタイム記 | ライピングや Lustre)の採用,及び制御プログラムの            |

| 憶・再生手法の開発   | キャッシュメモリ活用最適化で, <u>目標 128 チャンネル 1 時</u> |

|             | 間記憶。                                    |

| ③製品化に向けた実装  | 顧客に求められる製品化に向けて,                        |

| 技術          | 目標 従来比 1/10 程度の低コスト化製品の実現。              |

|             |                                         |

# [研究開発の年度目標]

| 区分        | 25年度(1年目)             | 26年度(2年目)             |

|-----------|-----------------------|-----------------------|

| ①データ圧縮と並列 | ○速度 200Mbyte/sec を達成す | ○速度 400Mbyte/sec を達成す |

| 制御システムの高  | る。                    | る。                    |

| 速化手法の開発   |                       |                       |

| ②多チャンネル大容 | ○64 チャンネルで 1 時間記憶     | ○128 チャンネルで 1 時間記     |

| 量データのリアルタ | を達成する。                | 憶を達成する。               |

| イム記憶・再生手法 |                       |                       |

| の開発       |                       |                       |

# ③製品化に向けた実 装技術

- -1 マルチ・ハイス ピードデータロガー の組立・調整

- -2 新たな電子機器 としての要求性能の 確立

- -3 モデルベース開発ツールとしての有効性の確立

# 3 - 1

64 チャンネルを実装するボードコンピュータを実現する。

(3) - 2

一般用電子機器の EMC 試験 による,ノイズへの耐性の実 力把握を行う。

(3) - 3

ラピッドコントロールプロト タイピング(RCP)環境の 構築。 3 - 1

128 チャンネルを実装する ボードコンピュータを実現す る。

(3) - 2

VCCI/IEC 規格への準拠を実現する。

3 - 3

本研究開発装置を用いたRC Pの実証試験と評価。

<u>目標 従来比 1/10 程度の低コ</u>スト化製品を実現する。

### (3) 実施内容

①データ圧縮と並列制御システムの高速化手法の開発

(担当実施機関:広島市立大学, ㈱広洋電子)

データ圧縮を行うために、ハフマン符号化法、LZ77、ブロックソート法、MTF (Move-to-Front)法を組み合わせたアルゴリズムにおける実際的なデータ圧縮量とそのための計算量を、既存の測定対象のデータを用いて比較する。正確な測定を行うために、サンプリング周期に比べて充分小さな周波数(例えば1周期に10サンプリング点以上)が対応可能周波数となる。このとき、毎回16ビットの数値を記憶するより前測定ポイントからの差分データを記録することで、ビット数を減少させることができ、これにより情報圧縮を行う。仮に16ビットの精度であれば、振幅65536×2の変化を10等分した値は14ビットで表すことができ、2ビット削減できる。

従来のシステムでは、データ転送経路の物理規格値に比べて、50%程度の実効転送能力しか実現できていない。OSのオーバヘッドが原因と考えられるが、システムトレースのソフトウェアツールを用いることで問題点を明確にすることができ、その対策を施した高速化した制御プログラムを組込むことにより、ハードウェアの物理規格値に近づける。オーバヘッドをゼロにすることは難しいが、25年度は制御プログラムの最適化により物理規格値の80%程度まで引き上げる。

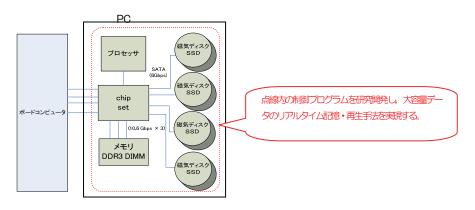

②多チャンネル大容量データのリアルタイム記憶・再生手法の開発

(担当実施機関:広島市立大学、㈱広洋電子)

前記①項と連動確認しながらの開発となる。

スーパーコンピュータで使用されるファイルシステム(Lustre)及びデータ送量拡大方式(RAIDO:ストライピング)を採用して実装,評価を行なう。また,主記憶をメモリ性能の限界付近で使用するためには,プロセッサに実装されているキャッシュメモリを効率よく使用することが重要である。このような,キャッシュメモリを活用し

た制御プログラムの最適化手法については、制御プログラムのメモリアクセスの振る舞いをシミュレータやプロファイラで解析する。その解析結果をもとに、データ構造の見直しや変数のメモリ割付けを変更するようにプログラムの実行論理を書き換えることで、最終目標(128 チャンネルで1時間記憶)を達成できるようにプログラムを最適化する。

#### ③製品化に向けた実装技術

(担当実施機関: (株広洋電子, (株石井表記, 広島県立総合技術研究所)

③-1 マルチ・ハイスピードデータロガーの組立・調整

(㈱広洋電子, ㈱石井表記)

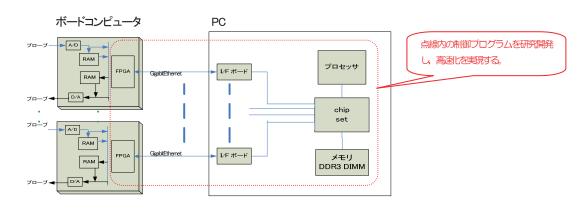

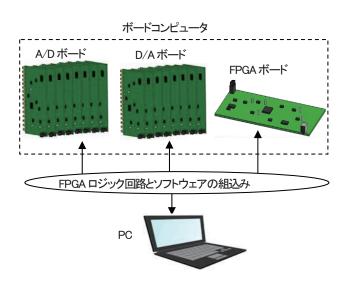

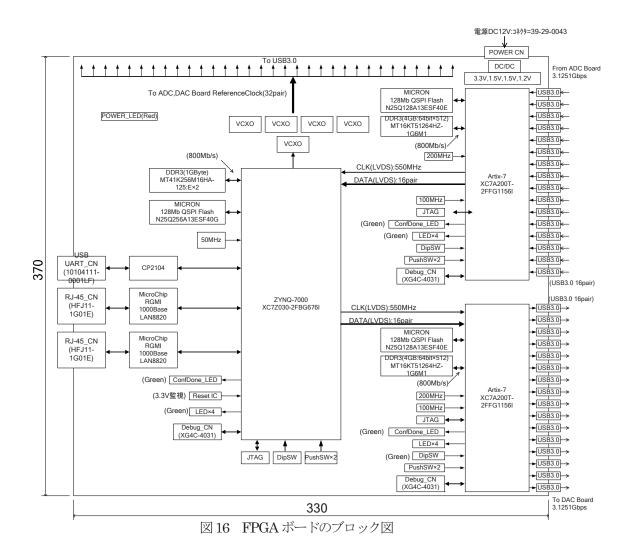

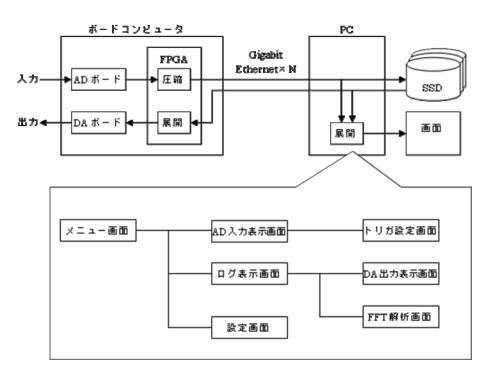

### 1) ハードウェア

A/D, D/A ボードに対して、FPGA ボードから共通の周波数クロックを供給し、同時サンプリングを保証するボードコンピュータにする。FPGA は、マイクロコンピュータを内蔵した Xilinx 社製を採用し、各 A/D、D/A ボードと FPGA ボード間のデータ転送は業界最大 3.125Gbps トランシーバ接続方式を採用する。

また、FPGA ボードと PC 間は、業界最高速の通信規格である GigabitEthernet 接続方式を採用し、128 チャンネル分のアナログデータを 高速に転送させるボードコンピュータ(A/D、D/A、FPGA ボード)の設計、製作、組立、調整を行う。併せて、ノイズへの耐性を考慮した筐体の設計、製作、組立、調整を行う。

## 2) ソフトウェア

128 チャンネル分の A/D/・D/A ボードでデータをバッファする FPGA ロジック回路を組込み,FPGA ボードで A/D・D/A ボードのデータをバッファしながらマイクロコンピュータで Gigabit Ethernet 通信を制御するソフトウェアの組込みと調整を行う。更に,Gigabit Ethernet 通信を制御し同時に SSD に対して記憶・読出し処理する PC ソフトウェアの組込みと調整を行う。

# ③-2 新たな電子機器としての要求性能の確立 (㈱広洋電子)

- 1)本研究開発装置が新たな電子機器として要求される性能(IEC 及び VCCI 規格の適合性)をトータルシステムで検証する為、オシロスコープを活用すると共に検証用 P C ソフトウェアを使用して実施する。必要に応じて、③-1 項へのフィードバックを行う。

- 2) 昨年度実施した EMC 試験結果より、以下に示す3項目が不合格であった為、 その項目について、EMC 試験を行い、ノイズへの耐性を評価、検証する。

- (1)放射エミッション測定

- (2)放射磁界イミュニティ試験

- (3)FTB 試験

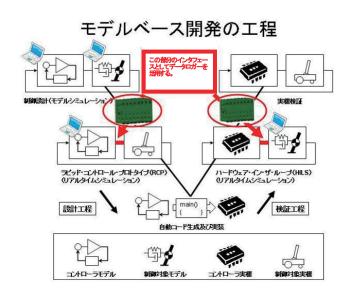

### ③-3 モデルベース開発ツールとしての有効性の確立

(広島県立総合技術研究所)

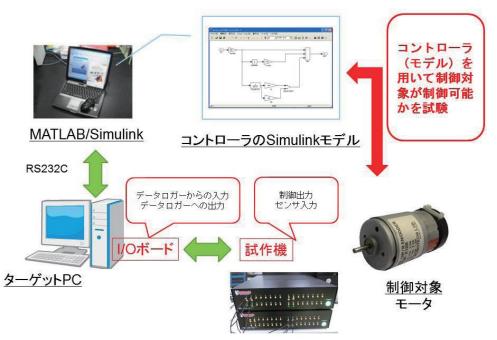

自動車の開発に標準的に用いられているモデルベース開発の工程のうち、敏速なコントローラモデルの実時間稼動による検証(ラピッド・コントロール・プロトタイピング: R C P) や、自動車ハードウェアコンポーネントの模擬環境中での試験(ハードウェア・イン・ザ・ループシミュレーション: H I L S) の際に、本研究開発装置の有効活用を検証する。

具体的には、シミュレーションを行うホストコンピュータと、実機またはCPUを繋ぐターゲットコンピュータとで構成するモデルベースシミュレーションシステムを用い、かつ実機またはCPUからターゲットコンピュータにデータを取り込むツールとして、本研究開発装置のマルチ・ハイスピードデータロガーを用いて、以下を行う。

- (1)ターゲットコンピュータのインタフェースドライバーとして本研究開発装置の有用性を検討・検証

- (2)本研究開発装置を用いたRCPとHILSの実証試験と評価

## ④プロジェクトの管理・運営(実施担当機関:公益財団法人ひろしま産業振興機構)

本研究開発の円滑な運営と推進を図るために、今年度は3回程度の推進委員会を開催し、研究開発の進捗のフォローと同時に設備の状況をチェックし、プロジェクトの推進管理を実施する。

また研究開発成果について、報告書作成の検討及びとりまとめを行う。

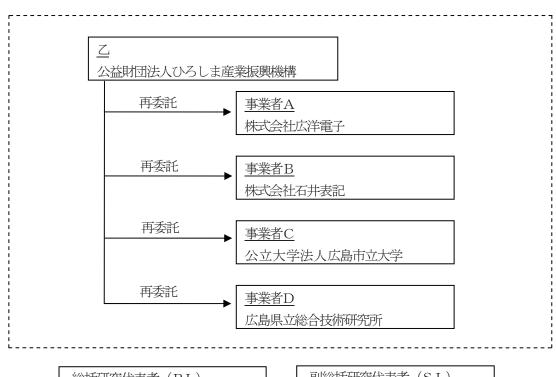

### 1-2 研究体制

(研究組織・管理体制,研究者氏名,協力者)

- (1) 研究組織及び管理体制

- 1)研究組織(全体)

総括研究代表者(PL) 株式会社広洋電子 三代 秀和 副総括研究代表者(SL) 株式会社広洋電子 津川 泰紀

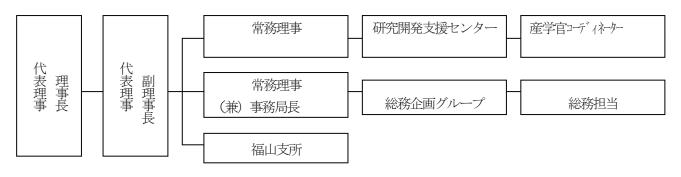

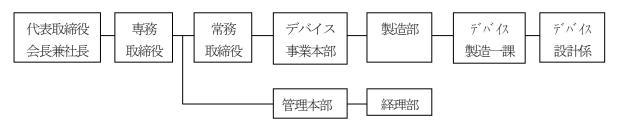

# 2) 管理体制

## ①事業管理機関

「公益財団法人ひろしま産業振興機構」

# ② (再委託先)

# 株式会社広洋電子

# 株式会社石井表記

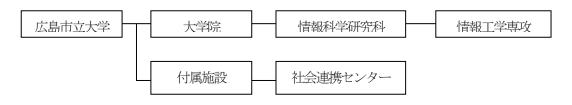

# 公立大学法人広島市立大学

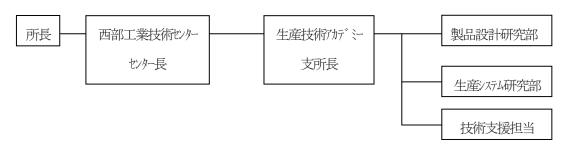

# 広島県立総合技術研究所

# (2) 管理員及び研究員

# 【事業管理機関】 公益財団法人ひろしま産業振興機構

# 管理員

| 氏 名                                                   | 所属・役職                                                                                                                                                       | 実施内容(番号)                                  |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 渡辺 博之<br>西村 和県 神郎 | 常務理事 研究開発支援センター 研究統括マネジャー 研究開発支援センター 研究開発推進マネジャー 研究開発支援センター 参事 研究開発支援センター 課長 研究開発支援センター 課長 研究開発支援センター 建長 研究開発支援センター 産学官コーディネータ 研究開発支援センター 主事 研究開発支援センター 推進員 | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4 |

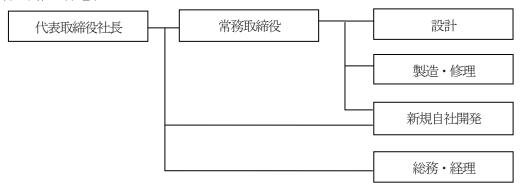

# 【再委託先】

# 株式会社広洋電子

| 氏 名   | 所属・役職       | 実施内容(番号)       |

|-------|-------------|----------------|

| 三代 秀和 | 新規自社開発 リーダー | ①, ②, ③-1, ③-2 |

| 沖本 勉  | 設計 スペシャリスト  | 3-1            |

| 津川 泰紀 | 設計          | ①, ②, ③—1      |

| 安藤 貴志 | 設計          | ①, ②, ③—1      |

| 吉野 正一 | 設計          | 3-2            |

| 櫨川 正樹 | 設計          | 3-1            |

| 上向井 毅 | 研究員         | 3-1            |

# 株式会社石井表記

|    | 氏 名 | 所属・役職       | 実施内容(番号) |

|----|-----|-------------|----------|

| 藤岡 | 俊明  | デバイス製造一課 課長 | 3-1      |

# 公立大学法人広島市立大学

|    | 氏 名 | 所属・役職             | 実施内容(番号) |

|----|-----|-------------------|----------|

| 北村 | 俊明  | 情報科学研究科 情報工学専攻 教授 | ①, ②     |

| 窪田 | 昌史  | 情報科学研究科 情報工学専攻 助教 | ①, ②     |

# 広島県立総合技術研究所

|    | 氏 名 |           | 所属・役職   |        | 実施内容(番号) |

|----|-----|-----------|---------|--------|----------|

| 門藤 | 至宏  | 生産技術アカデミー | 製品設計研究部 | 部長     | 3-3      |

| 倉本 | 丈久  | 生産技術アカデミー | 製品設計研究部 | 副主任研究員 | 3-3      |

### (3) 経理担当者及び業務管理者の所属、氏名

(事業管理機関)

公益財団法人ひろしま産業振興機構

(経理担当者)研究開発支援センター 参事 神田 敏和 (業務管理者)常務理事 渡辺 博之

# (再委託先)

株式会社広洋電子

(経理担当者) 代表取締役社長 平井 將宗 (業務管理者) 常務取締役 佐伯 岳

# 株式会社石井表記

(経理担当者) 経理部

経理部

係長

壇上

和則

(業務管理者) 製造部

部長

藤尾

茂

### 公立大学法人広島市立大学

(経理担当者) 社会連携センター 佐藤 真帆 (業務管理者) 情報科学研究科 科長 教授 矢野 卓雄

# 広島県立総合技術研究所

(経理担当者) 西部工業技術センター 生産技術アカデミー 技術支援担当 副主任研究員 馬場 祥宏 (業務管理者) 西部工業技術センター 生産技術アカデミー 支所長 打田 澄雄

# (4) 他からの指導・協力者

| 氏名     | 所属・役職                                  | 備考          |

|--------|----------------------------------------|-------------|

| 末繁 惠一郎 | マツダ株式会社<br>パワートレイン開発本部<br>アシスタントマネージャー | 推進委員会アドバイザー |

| 川畑 敬志  | 広島工業大学<br>名誉教授                         | 推進委員会アドバイザー |

| 天野 康範  | 株式会社PALTEK<br>西日本支社 課長                 | 推進委員会アドバイザー |

# 1-3 成果概要

開発テーマごとの成果の概要は次表のとおりである。

| 開発アーマことの収集の概要は次本開発テーマ                                         |                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 開発テーマ ①データ圧縮と並列制御システムの高速化手法の開発 ②多チャンネル大容量データのリアルタイム記憶・再生手法の開発 | 成果の概要  A/D 変換後のデータ転送およびSSD への格納速度の検証にて、擬似的なデータ供給プロセスからの転送で100MByte/sec 程度の転送速度が、RAW パケットフォーマットを使用することで得られた。一方、A/D 変換ボートからでは、7~11MByte/sec 程度となった。この要因は FPGA(CPU)ボード側の性能不足によるものであり、その原因を分析する道筋は立っていることから、その調査に従って目標達成への対策は検討・実施できる状態にある。  ① で構築したシステムにおいて、擬似的なデータ供給プロセスでの転送・格納を1時間程度継続可能か検証した。6 チャネル分程度ではあるが、1時間の記録を確認した。また、128 チャネルに拡張することを考え、複数のコンポーネントによる並列処理となっても単一の高速ファイルシステムを構築可能なはませてファ |

| ③-1 マルチ・ハイスピード<br>データロガーの組立・調整                                | イルシステムを試験的に構築しこれを用いて拡張可能であることを検証した。<br>目的とした 128 チャンネル仕様のボードコンピュータ<br>(A/D, D/A, FPGA ボード)と筺体、PC ソフトウェアの設計・製作・組立・調整を完了した。                                                                                                                                                                                                                                                                     |

| ③-2 新たな電子機器としての<br>要求性能の確立                                    | 昨年度のEMC 試験で不合格であった放射エミッション測定・放射電磁界イミュニティ試験・FTB 試験を実施した。結果として、放射電磁界イミュニティ試験は合格。放射エミッション測定と FTB 試験は再度不合格となった。また、昨年度は放射電磁界イミュニティ試験・FTB 試験で、ノイズの影響によりボードコンピュータ(A/D, D/A, FPGAボード)の一部が故障したが、本年度は、故障は発生していない為、耐ノイズ性の向上は見受けられた。                                                                                                                                                                      |

|                                                               | これらの対応については、ボードコンピュータ(A/D, D/A, FPGA ボード)の電源にコンデンサ挿入等を行い、ボードそのもののノイズ耐性を上げる必要があると考える。また、放射エミッションの妨害波抑制については、ボードコンピュータ(A/D, D/A, FPGA ボード)の IC チップに電磁波シールド材を使用する事と、筐体材料を電磁波シールド効果に優れているアルミに変更する事で何処まで妨害波を抑制できるかを検討する必要があると考える。                                                                                                                                                                  |

| ③-3 モデルベース開発ツール<br>としての有効性の確立                                 | 試作したマルチ・ハイスピードデータロガーを用いたラピッドコントロールプロトタイピング環境を構築するとともに、構築した環境を用いたフィードバック制御試験が可能であることが確認できた。一方で、出力信号が減衰するなど、実用上の問題があることが判明した。実用化に当たっては、これら問題点の解決が必要である。                                                                                                                                                                                                                                         |

# 1-4 当該研究開発の連絡窓口

# (1) 事業管理機関

公益財団法人ひろしま産業振興機構

研究開発支援センター 参事 神田 敏和

〒730-0052 広島県広島市中区千田町三丁目7番47号 広島県情報プラザ

TEL: 082-240-7712 FAX: 082-242-7709

E-Mail:t-kanda@hiwave.or.jp

# (2) 研究実施機関

# 株式会社広洋電子

プロジェクトリーダ 三代 秀和

〒733-0005 広島県広島市西区三滝町16番5号

Tel: 082-238-0407/082-239-3969

Fax: 082-238-6358

E-Mail: h.mishiro@koyo-densi.co.jp

## 第2章 本論

1 データ圧縮と並列制御システムの高速化手法の開発

### (1)研究内容

最大 128 チャンネルから送り込まれる 400MByte/sec のデータを SSD などの記憶装置にリアルタイムで蓄積し、各測定ポイントのデータの同期を保証すると共に、従来のデータロガーには存在しない「記憶データをアナログ信号出力として再現(リプレイ)する新しい機能」を備えたマルチ・ハイスピードデータロガー(計測装置)を開発する。

本研究では、このマルチ・ハイスピードデータロガーについて、A/D 変換後のデータを SSD に格納、および SSD に格納されたデータを D/A 変換部に転送の両方向転送のデータ転 送速度の達成を確立するべく、次の内容について研究を行う。

- ○転送速度を等価的に向上させるためのデータ圧縮

- ○A/D 変換後のデータ転送および SSD への格納速度の検証

### (2) 研究方法

①転送速度を等価的に向上させるためのデータ圧縮

昨年度の研究成果により、100kHz 台では 30%程度、20kHz 台では 50%程度の圧縮効果が期待できることが分かっている。また、この圧縮を行うためのハードウェア構成についても検討済みである。

# ②A/D 変換後のデータ転送および SSD への格納速度の検証

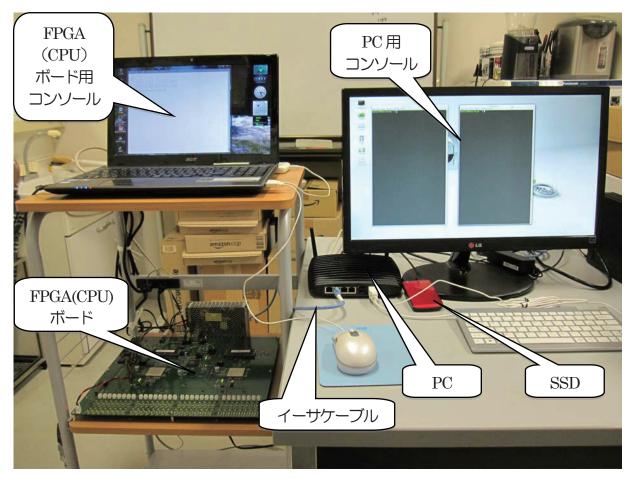

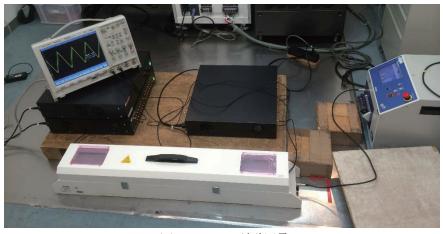

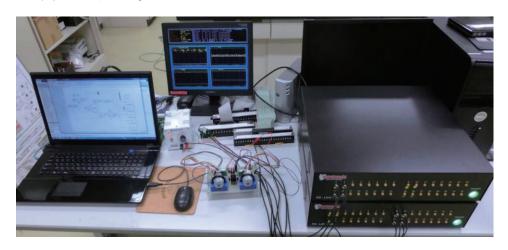

昨年度は、FPGA(CPU)ボードが調整中のため、実際に接続して転送能力測定は行えず、PC上で折り返しデータの転送を行なうプログラムで、転送速度を測定した。今年度は、FPGA(CPU)ボードを使用することができたため、実際に接続して転送能力測定を行った。なお、FPGA(CPU)ボードにおいても PC と同様の Linux OS (ただし、ハードウェア構成の都合で PC 側のものと比べると機能制約のかかった縮小構成のもの) が搭載されており、折り返し時に使用したプログラムをそのまま移植可能であった。表1に使用した FPGA(CPU)ボード上のプロセッサ構成を、表2に使用した PC を示す。図1には、測定環境を示す。

| 表1 | 使用した FPGA(CPU)ボード |

|----|-------------------|

|    |                   |

|                  | ZYNQ XC7Z030-2FBG676I                                       |  |

|------------------|-------------------------------------------------------------|--|

| CPU              | ARM A9 dual core 800MHz                                     |  |

| RAM              | DDR3-1066 dual channel (two SO-DIMM) 8GB                    |  |

| GbE Controller   | LAN: Microchip LAN8820                                      |  |

| Controller clock | EMIO gigabit Ethernet controller maximum frequency = 125MHz |  |

| DMA clock        | DMA maximum frequency = 100MHz                              |  |

| OS               | PetaLinux v2013.10 (Yocto 1.4)                              |  |

#### 表2 使用したPC

|         | Intense PC                                          |  |

|---------|-----------------------------------------------------|--|

| CPU     | Intel Core i7-3517UE 64bit dual core 1.7GHz 17W TDP |  |

| RAM     | DDR3-1333 dual channel (two SO-DIMM) 8GB            |  |

| 内蔵 DISK | 2.5" hard disk 500GB 6Gbit/sec                      |  |

| 外付け SSD | Buffalo SSD-PE128U3-RD USB3.0 接続 128GB              |  |

|                | LAN1: Intel 82579 GbE PHY (MAC integrated into the chipset) |  |

|----------------|-------------------------------------------------------------|--|

| GbE Controller | LAN2: Realtek RTL8111F-CG GbE controller                    |  |

|                | LAN3-6: Intel 82574 GbE Controller                          |  |

|                | Linux Mint 13: maya(x86-64)                                 |  |

| OS             | Kernel: 3.20-35-generic                                     |  |

|                | Build: #55-Ubuntu SMP Wed Dec 5 17:42:16 UTC 2012           |  |

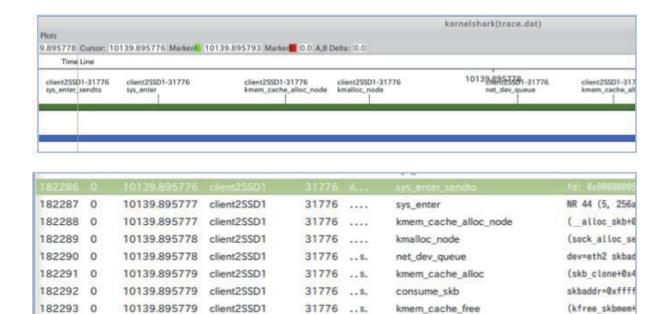

図 1 測定環境

図1に測定環境を示す。図1中央の黒い箱が使用した PC であり、フロントパネルにはギガビットイーサネットのポートが4基搭載されている。また、図1左下の基板が FPGA(CPU)ボードであり、奥側にギガビットイーサネットのポートがある。これと PC のフロントパネルのポートをクロスケーブルで直結した。図1中央部、PC の右側に外部 SSD 装置を用意し、PC 裏側の USB3 ポートと接続してある。 FPGA(CPU)ボード上には、ギガビットイーサネットのポートが2個用意されており、最大2系統で、FPGA(CPU)ボードと PC 間を接続できる。

FPGA(CPU)ボードで計測データ相当のデータをパケットに仕立てて、PC に送信する。PC 側では、パケットを待ち受けるプロセスを動作させているので、送られてきたパケットを受信し、送られてきたパケットのデータを SSD に書き込む別プロセスを立ち上げるだけで、受信を報告(応答パケットを送信)して、次のパケットの受信に備える。SSD への書き込みを別プロセスに行わせることで、イーサネットの通信速度低下を防いでいる。

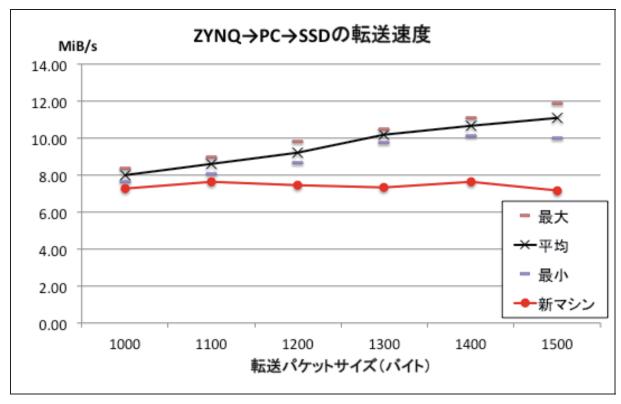

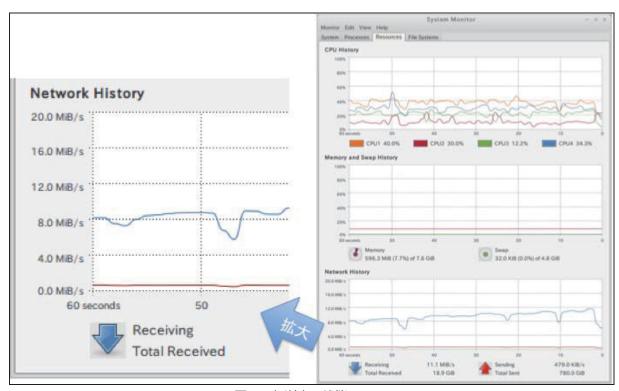

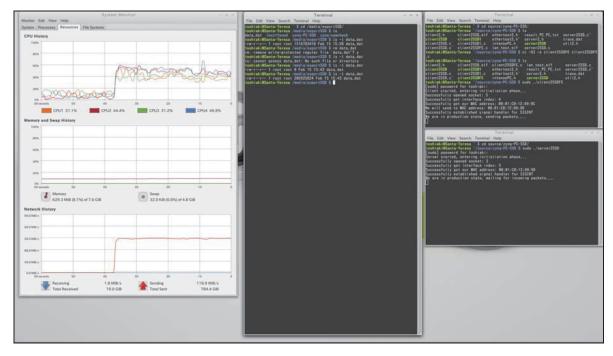

図2に測定結果、図3に、測定中のシステム状況をシステムモニターの画面で示す。なお、改版した FPGA(CPU)ボードと新筐体に内蔵される PC の組み合わせにおいても、同じプログラムを走行させて測定した。

図 2 測定結果

図3 転送中の状態

測定結果からわかる通り、FPGA(CPU)ボードからの転送では、 $8\sim1~1~MB$ yte/sec 程度しか、転送スピードが出ていない。実際、システムモニターの示す値もその程度である。また、改版した FPGA(CPU)ボードと管体に組み込む PC との転送でも $7\sim8~MB$ yte/sec 程度となった。そこで、FPGA(CPU)側の問題か PC 側の問題かを切り分けるために、 $PC\rightarrow PC\rightarrow SSD$  の転送形態で同じプログラムを走行して測定を行った。その結果を図4、測定中のシステムモニターを図5に示す。

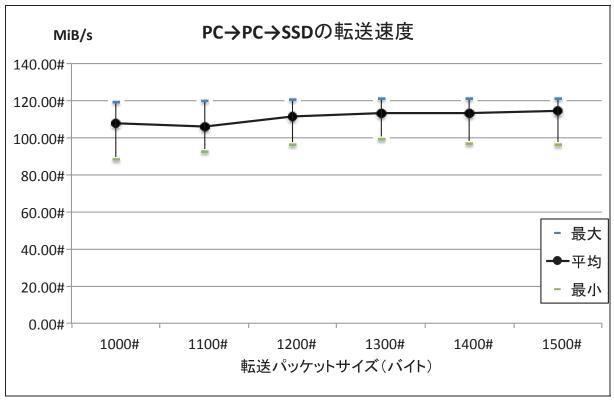

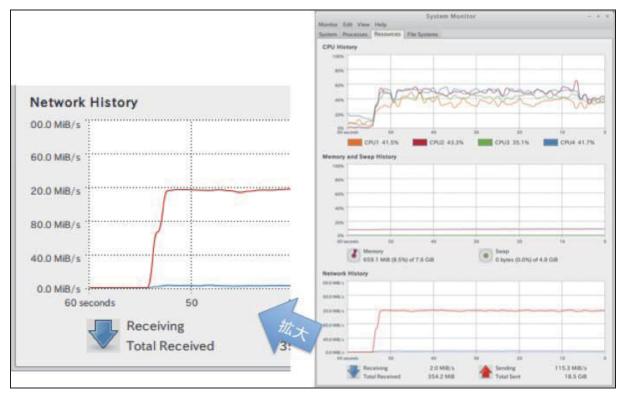

図 4 【比較】PCからの転送

図 5 【比較】PCからの転送中の状態

図4、5から分かるように、PC から同じプログラムで転送を行うと $100\sim120$  MByte/sec の転送速度が得られており、これは、 $800\sim960$  Mbit/sec となってほぼギガビットイーサネットの限界値である。このため、転送速度が出ていないのは、FPGA(CPU)ボード側の問題と考えられる。

この原因として考えられるのは、

- ZYNQ側のネットワークアダプタチップの実行性能不足

- **ZYNQ** のメモリ転送能力不足(100MHz・4/8バイトバス)

- ZYNQ用 Linux のドライバがハード性能を使いきれていない

- ZYNQ用 Linux 自体のオーバヘッド

である。この切り分けに関しては、Linux に付属している ftrace 機能を用いて詳細な動作を確認することで可能である。ただ、現在インストールされている Linux ではメモリ資源などの制約から、この機能を不活性化したカーネルを用いているため、カーネル再構築する必要があり、期間内には調査ができなかった。PC 側の Linux では機能が活性化されており、ftrace を取得できたので、この動作と比較することで、原因の究明は可能と考える。また、原因が判明すれば、ここで使われている CPU は FPGA 部分を持ったものであり、容易に機能のハードウェア化が可能である。このことにより、期限内に目標性能を達成することはできなかったが、目標達成への道筋は立ったと考える。図6に取得したトレースの一部を例として示す。

図 6 ftrace で取得したイベント

31776 ..s.

31776 d...

net\_dev\_xmit

sys\_exit\_sendto

dev=eth2 skbad

0x5ea

## (3) 結果と考察

182294 0

182295 0

①転送速度を等価的に向上させるためデータの圧縮

圧縮効果を確認でき、またそれを実現する回路についても検討した。この技術を活用できると考える。

②A/D 変換後のデータ転送および SSD への格納速度の検証

10139.895780 client2SSD1

10139.895780 client2SSD1

FPGA(CPU)ボード側の性能不足が明らかとなったが、その原因を分析する道筋は立っており、その調査に従って、目標達成への対策は検討・実施できる状態にある。

### 2 多チャンネル大容量データのリアルタイム記憶・再生手法の開発

### (1) 研究内容

最大 128 チャンネルから送り込まれる 400MByte/sec のデータを SSD などの記憶装置にリアルタイムで蓄積し、各測定ポイントのデータの同期を保証すると共に、従来のデータロガーには存在しない「記憶データをアナログ信号出力として再現(リプレイ)する新しい機能」を備えたマルチ・ハイスピードデータロガー(計測装置)を開発する。

本研究では、スーパーコンピュータで使用されるファイルシステム(Lustre)及びデータ送量拡大方式(RAIDO:ストライピング)を採用して実装、評価を行なう。別紙1で述べた「データ圧縮と並列制御システムの高速化手法の開発」と連動しながら、転送されたデータを、転送速度を妨げることなく記憶装置に格納できることを目標に開発を行った。

### (2) 研究方法

通常の USB 接続の SSD 装置にどのくらいの書き込み速度でデータを格納できるかを測定するために、別紙1の環境に併設した。書き込み速度としては、別紙1の資料に示したように、ギガビットイーサネット 1本の帯域をほぼフルに使用した状態でも、書き込みを別プロセスに投げることで並列処理を行い、転送に影響を与えることがないことを確認した。

また、128 チャネルで1時間の記録が可能なことを検証するために1時間の測定を行った。FPGA (CPU) ボードが調整中のため、実際に128 チャネルを測定することはできなかったが、PC—PC の転送を行い、1500 バイトのパケットで最大転送レートを作って1時間の書き込みを行った。この環境がどのくらいのチャネル数になるかは、測定する波形の周波数により圧縮率が異なるため、一概には言えないが、サンプリングが20 MHz、1 サンプルあたり2 バイトであるため、全く圧縮しないと40 MB/sec となる。20 kHz 台では50%程度の圧縮効果が得られることから、仮に50%の圧縮率が得られたとすると、1 チャネルあたり20 MB/sec となり、ギガビットイーサネット1 本あたりで6 チャネル分の転送量となる。この測定の様子を図7~8 に示す。

図 7 データ格納能力測定の様子

```

Terminal

File Edit View Search Terminal Help

toshiaki@Santa-Teresa * $ cd /media/exportSSD/

toshiaki@Santa-Teresa /media/exportSSD $ ls

data.dat lost+found zynq-PC-SSD zynq-sumcheck

toshiaki@Santa-Teresa /media/exportSSD $ ls -l data.dat

-rw-r--r-- 1 root root 1516783418 Feb 15 15:28 data.dat

toshiaki@Santa-Teresa /media/exportSSD $ rm data.dat

rm: remove write-protected regular file 'data.dat'? y

toshiaki@Santa-Teresa /media/exportSSD $ ls -l data.dat

ls: cannot access data.dat: No such file or directory

toshiaki@Santa-Teresa /media/exportSSD $ ls -l data.dat

-rw-r--r-- 1 root root 0 Feb 15 15:43 data.dat

toshiaki@Santa-Teresa /media/exportSSD $ ls -l data.dat

-rw-r--r-- 1 root root 206925824 Feb 15 15:43 data.dat

toshiaki@Santa-Teresa /media/exportSSD $ ls -l data.dat

-rw-r--r-- 1 root root 3000655872 Feb 15 15:44 data.dat

toshiaki@Santa-Teresa /media/exportSSD $ ls -l data.dat

-rw-r--r-- 1 root root 3011907584 Feb 15 15:44 data.dat

toshiaki@Santa-Teresa /media/exportSSD $ ls -l data.dat

-rw-r--r-- 1 root root 4732329984 Feb 15 15:46 data.dat

toshiaki@Santa-Teresa /media/exportSSD $ ls -l data.dat

-rw-r--r-- 1 root root 73910235136 Feb 15 16:27 data.dat

toshiaki@Santa-Teresa /media/exportSSD $ ls -l data.dat

-rw-r--r-- 1 root root 93118840832 Feb 15 16:41 data.dat

toshiaki@Santa-Teresa /media/exportSSD $ ls -l data.dat

-rw-r--r-- 1 root root 93839908864 Feb 15 16:41 data.dat

toshiaki@Santa-Teresa /media/exportSSD $ ls -l data.dat

-rw-r--r-- 1 root root 95949594624 Feb 15 16:42 data.dat

toshiaki@Santa-Teresa /media/exportSSD $ ls -l data.dat

-rw-r--r-- 1 root root 98869796864 Feb 15 16:44 data.dat

toshiaki@Santa-Teresa /media/exportSSD $

```

図 8 データ格納能力測定の進行

図 7 に示すように転送中の CPU 負荷は、確保艶 5 0%程度で、処理能力としては、ギガビットイーサネットをもう 1 本ぐらい接続しても問題なさそうである。また図 8 に示すように、ほぼ 1 時間の転送で、9 8 GByte 程度のデータが書き込まれた。

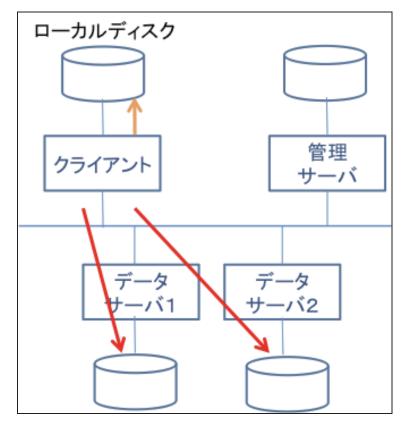

ギガビットイーサネット1本での測定はできたが、128チャネル分となると環境が整えられないので、複数システムの並列動作が可能であることの検証に、Lustre ファイルシステムを構築して、その挙動を測定した。このファイルシステムは、ネットワーク接続された複数のシステムを横断して構築される見かけ上単一となるファイルシステムであり、スーパーコンピュータシステムなどで使われている。図9に構成したシステムの構成図を示す。

図 9 Lustre ファイルシステムの構成

プロセスは逐次処理で、419MBのデータを1回書き込み10回読み出す動作を行う。この時、ローカルディスクに対しては、6.171Gbit/secの転送速度であったが、Lustre並列I/Oに対しては、ギガビットイーサネットの限界値である1.028Gbit/secの転送速度を得られた。このことから、複数システムで128チャネルシステムを構成することになっても、ファイルシステムが各サブシステムごとに分断されることなく、統一的なファイルシステムとして提供できる見通しができた。

### (3) 結果と考察

リアルタイムの記憶・再生手法について検討を行い、実際に128チャネルの測定環境を構築することはできなかったが、6チャネル分程度で1時間の測定は可能なことを実証でき、これを128チャネル化する拡張についても、Lustre ファイルシステムを活用した方式を用いることで、十分実現可能であることが検証できた。

- 3 製品化に向けた実装技術

- 3-(1) マルチ・ハイスピードデータロガーの組立・調整

#### (1)研究内容

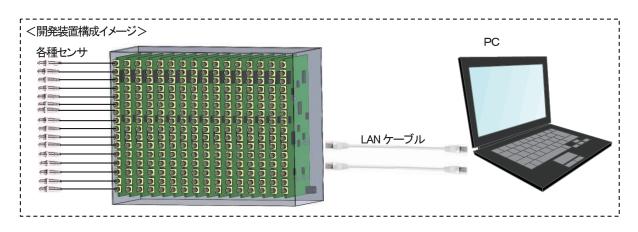

最大 128 チャンネルから送り込まれる 400MByte/sec のデータを SSD などの記憶装置にリアルタイム で蓄積し、各測定ポイントのデータの同期を保証すると共に、従来のデータロガーには存在しない「記憶 データをアナログ信号出力として再現(リプレイ)する新しい機能」を備えたマルチ・ハイスピードデータロガー(計測装置)を開発する。

本研究では、製品化に向けた実装技術について、マルチ・ハイスピードデータロガーの中枢となる 128 チャンネル仕様のボードコンピュータ (A/D,D/A,FPGA ボード,ソフトウェアの組込み) の設計・製作・組立・調整を行う。併せて、ノイズへの耐性を考慮した設計、製作を行う。

- ○筐体の設計・製作

- ○128 チャンネル仕様 A/D ボードの設計・製作・組立・調整

- ○128 チャンネル仕様 D/A ボードの設計・製作・組立・調整

- ○128 チャンネル仕様 FPGA ボードの設計・製作・組立・調整

- ○128 チャンネル仕様ボードコンピュータへのソフトウェアの組込み・調整

### (2) 研究方法

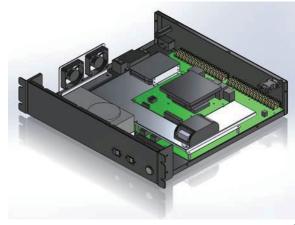

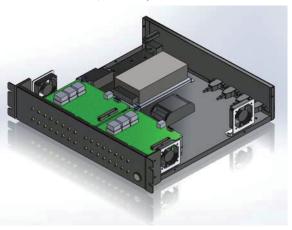

①筐体の設計・製作

下記の仕様にて筐体設計は3次元CADを使用し行った。CADはSolidWorksを用いた。 19 インチラック JIS-2J サイズを適用し、A/D,D/A,FPGA ボードを個々に共通の筐体サイズでユニット化。

- ・FPGA ボードを内蔵したメインユニット

- ・A/D, D/A ボードを各4枚 (32 チャンネル) を内蔵したサブユニット

筐体サイズ : 430(W)×430(D)×99(H)mm (両ユニット共通)

搭載部品 : メインユニット

・FPGA ボード 1枚・電源周辺部品 1式

サブユニット

·A/D (D/A) ボード 4枚

•雷源周辺部品 1式

図10 製品イメージ

その他: ユニット側面にL金具を取り付ける事でラックマウントが可能

ユニット単体でも積み上げられ、オープンマウントでも使用が可能

32 チャンネルの倍数で最大 128 までを自由に選択が可能

A/D・D/A ボードはカバーを取り外すことで容易に交換が可能

ノイズ耐性を考慮した金属ケース

# ○概観

サブユニット

図11 概観

メインユニット

サブユニット

図12 内部概観

ラックマウント (128 チャンネル) オープンマウント (64 チャンネルイメージ)

図13 実使用概観

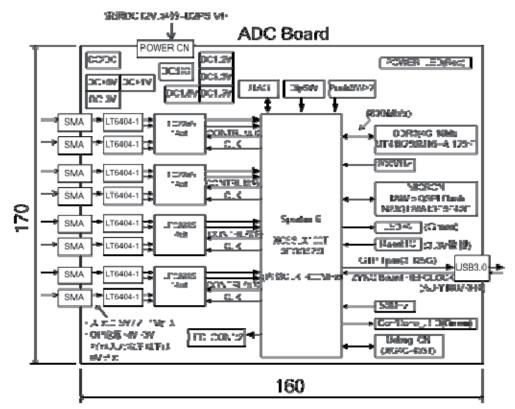

- ②128 チャンネル仕様 A/D ボードの設計・製作・組立・調整

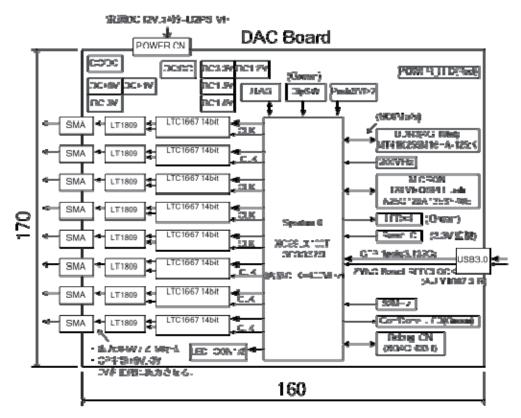

- ③128 チャンネル仕様 D/A ボードの設計・製作・組立・調整

- ④128 チャンネル仕様 FPGA ボードの設計・製作・組立・調整

- ⑤128 チャンネル仕様ボードコンピュータへのソフトウェアの組込み・調整 表 3 に示す仕様にてボードコンピュータ (A/D,D/A,FPGA ボード) を設計・製作し、組込みソフトウェアを実装した。

表3 ボードコンピュータ仕様

| See a language between the second sec |                                            |                                                                                  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------|--|--|

| 項目                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 主要部品など                                     | 仕様                                                                               |  |  |

| A/D ボード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FPGA:XC6SLX100T·3FGG676I,<br>ADC:LTC2285×4 | 入力 Z:1MΩ,入力電圧 0-5V                                                               |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            | AD 変換 14bit 以上,帯域 20MHz 以上<br>基板製作枚数:16 枚                                        |  |  |

| D/A ボード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FPGA:XC6SLX100T-3FGG676I,<br>DAC:LTC1667×8 | 出力 <b>Z</b> =50 <b>Q</b> ,出力電圧 0-5V<br>DA 変換 14bit 以上,帯域 20MHz 以上<br>基板製作枚数:16 枚 |  |  |

| FPGA ボード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | FPGA:XC7A200T·2FFG1156I×2,                 | 1000BaseLAN8820 2 <i>V</i> − <i>V</i>                                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | XC7Z030-2FBG676I                           | 基板製作枚数:2枚                                                                        |  |  |

| ボード設計                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                          | 基板回路設計,FPGA ロジック回路設計                                                             |  |  |

| ボード製造(組立)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                          | 部品実装(基板製造は外注)                                                                    |  |  |

| 組込みソフトウェア                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 仕様 OS:Linux                                | Ethernet:RawSocket(802.3Raw)                                                     |  |  |

図14 A/D ボードのブロック図

図15 D/A ボードのブロック図

図17 組込みソフトウェアの構成ブロック図と画面遷移図

#### (3) 結果と考察

#### ①筐体の設計・製作

金属(アルミおよび鉄)にて製作することで電源周辺および各ボードより発生するノイズを遮蔽。外部からのノイズの影響も受けにくい構造とした。また各部品は筐体のFGに以下の方法にて接続することにより筐体から外部へ逃がす構造とした。

# ○FGの接地方法

- ・A/D・D/A ボード・FPGA ボードは基板の取付穴より筐体の金属ボスにネジにて締め付け。

- ・電源部品はFG 端子よりケーブルにて筐体の金属ボスに接続。

筐体はラックマウントサイズの為、容易に持ち運びでき、またゴム足を付けることで、筐体を傷つけることなく接地することが可能である。19 インチのラックマウントに対応しており、付属のL金具を付けることで、ラックへの取付けが容易に行える。A/D・D/A ボードについては32 チャンネルの1ユニットタイプとなっており32 チャンネル毎に増設が可能で、最小で32 チャンネルから、その倍数で最大128 チャンネルまでが自由に選択可能である。

ユニットはカバーを取り外すことで A/D,D/A ボードの交換、取外しが可能であり、メンテナンスが容易な構造である。

②128 チャンネル仕様ボードコンピュータ (A/D,D/A,FPGA ボード) の設計・製作・組立・調整 表 1 に示すボードコンピュータの仕様に基づいて、128 チャンネル仕様のボードコンピュータ (A/D,D/A,FPGA ボード) の設計・製作・組立・調整を行った。製作したボードコンピュータの写真を 図 18~図 20 に示す。

図18 A/D ボード

図 19 D/A ボード

図20 FPGAボード

表4 製作したボードコンピュータ

|          | 製作枚数 | 製作したチャンネル数    | 備考                  |

|----------|------|---------------|---------------------|

| A/D ボード  | 16枚  | 128ch         | ボード 1 枚あたり 8ch 仕様   |

| D/A ボード  | 16枚  | 128h          | ボード 1 枚あたり 8ch 仕様   |

| FPGA ボード | 2枚   | 128ch を 2 セット | ボード 1 枚あたり 128ch 仕様 |

図21 筐体組込

図 22 MAIN ユニット内部 (FPGA ボード)

図 23 SUB ユニット内部 (A/D,D/A ボード)

# ③128 チャンネル仕様ボードコンピュータへのソフトウェアの組込み・調整

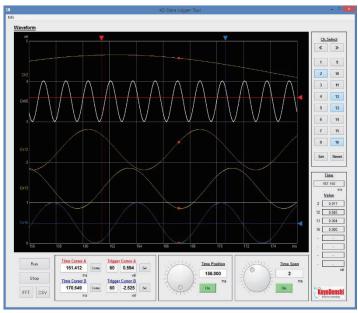

ボードコンピュータから送られてくる GigabitEthernet 通信データを受け取り SSD へ保存する PC ソフトと保存圧縮データを展開・閲覧可能なソフトを併せて作成し、検証用のソフトウェアの準備を完了した。

また, A/D 変換後のデータ圧縮と転送のためのダブルバッファ構成のソフトウェアを,図 17 に示す組込みソフトウェアの構成ブロック図内の圧縮部に組込みも完了した。

図24 検証用モニターソフトウェア画面

# (4) まとめ

目的とした 128 チャンネル仕様のボードコンピュータ (A/D,D/A,FPGA ボード)、筺体、PC ソフトウェアの設計・製作・組立・調整を完了した。

### 3-② 新たな電子機器としての要求性能の確立

#### (1)研究内容

最大 128 チャンネルから送り込まれる 400MByte/sec のデータを SSD などの記憶装置にリアルタイムで蓄積し、各測定ポイントのデータの同期を保証すると共に、従来のデータロガーには存在しない「記憶データをアナログ信号出力として再現(リプレイ)する新しい機能」を備えたマルチ・ハイスピードデータロガー(計測装置)を開発する。

本研究では、製品化に向けた実装技術について、新たな電子機器としての要求性能の確立を図るべく、 昨年度不合格であった EMC 規格(VCCI,IEC61000)に準じた EMC 試験と分析を行う。

# (2) 研究方法

昨年度、不合格であった VCCI 規格と IEC61000 規格に準じた EMC 試験を実施した。実施試験場として、(株)広島テクノプラザ 電波暗室・シールド室を利用した。試験の様子を図 25~図 27 に示す。

表5 EMC 試験内容

| 測定及び試験名                    | 規格           | 備考    |

|----------------------------|--------------|-------|

| 放射エミッション測定                 | VCCI         | クラス A |

| 放射電磁界イミュニティ試験              | IEC61000-4-3 | レベル3  |

| FTB (ファーストトランジェント・バースト) 試験 | IEC61000-4-4 | レベル3  |

図 25 放射エミッション測定風景

図 26 放射電磁界イミュニティ試験風景

図27 FTB試験風景

### (3) 結果と考察

EMC 試験結果を表6に示す。主な問題点は次のとおりである。

- ○放射エミッション測定と FTB 試験で不合格である。

- ○ボードコンピュータ (A/D,D/A,FPGA ボード) が IEC61000 規格のノイズの影響により誤動作が 発生し、また、放射レベルが VCCI 規格の許容範囲を超える結果となった。

表6 EMC 試験結果

| 測定及び試験名       | 規格           | 結果                     |

|---------------|--------------|------------------------|

| 放射エミッション測定    | VCCI         | 25MHz の逓倍周波数等で不合格      |

| 放射電磁界イミュニティ試験 | IEC61000-4-3 | 合格                     |

| FTB試験         | IEC61000-4-4 | A/D,D/A,FPGA ボードで誤動作発生 |

|               |              | 一部不合格                  |

結果より、ボードコンピュータ(A/D,D/A,FPGA ボード)の電源にコンデンサ挿入等を行い、ボードそのもののノイズ耐性を上げる事が必要と考える。

また、放射エミッションの妨害波抑制については、ボードコンピュータ(A/D,D/A,FPGA ボード)の IC チップに電磁波シールド材を使用する事と、筐体材料を電磁波シールド効果に優れているアルミに変更 する事で何処まで妨害波を抑制できるかを検討する必要があると考える。

今後は、補完研究として前述の通りに対応方法を検討し、対策を実施していく。

#### 3-3 モデルベース開発ツールとしての有効性の確立

### (1)研究内容

最大 128 チャンネルから送り込まれる 400MByte/sec のデータを SSD などの記憶装置にリアルタイム で蓄積し、各測定ポイントのデータの同期を保証すると共に、従来のデータロガーには存在しない「記憶 データをアナログ信号出力として再現(リプレイ)する新しい機能」を備えたマルチ・ハイスピードデータロガー(計測装置)を開発する。

本研究では、このマルチ・ハイスピードデータロガーについて、モデルベース開発ツールとしての有効性の確立を図るべく、次の内容について検討を行う。

- ○マルチ・ハイスピードデータロガーを用いたデータ入出力試験

- ○マルチ・ハイスピードデータロガーを経由したリアルタイムシミュレーション試験

#### (2) 研究方法

### ①マルチ・ハイスピードデータロガーを用いたデータ入出力試験

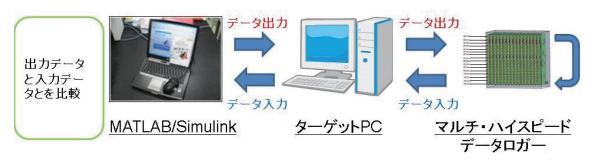

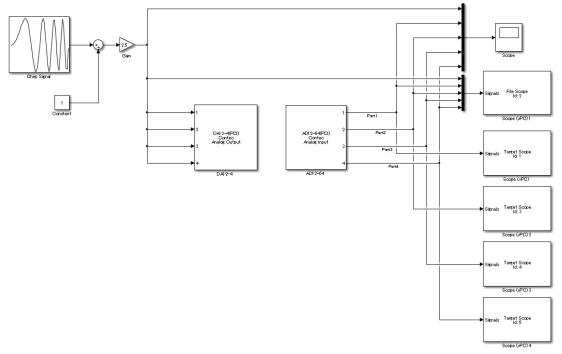

試作したマルチ・ハイスピードデータロガーのリアルタイムシミュレーションへの利用可能性を評価するため、データの入出力試験を行う。図 28 のとおり、シミュレータ(MATLAB/Simulink)からターゲットPCを経由してマルチ・ハイスピードデータロガーに信号を入力する。マルチ・ハイスピードデータロガー内で入力された信号をバイパスし、出力ポートから出力する。この出力信号をAD変換ポートに入力し、MATLAB/Simulink 上で入出力信号の比較を行うことで、信号の遅延や電圧の差を調査し、マルチ・ハイスピードデータロガーを用いたリアルタイムシミュレーションが可能かどうかを評価する。

図28 マルチ・ハイスピードデータロガーを用いたデータ入出力試験

#### ②マルチ・ハイスピードデータロガーを経由したリアルタイムシミュレーション試験

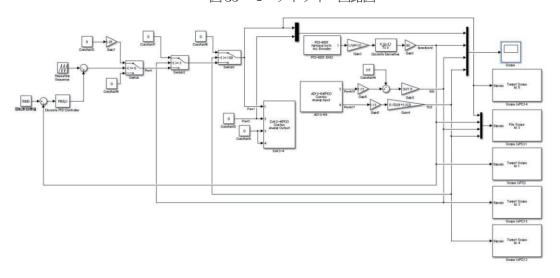

試作したマルチ・ハイスピードデータロガーを用いてモデルベース開発におけるリアルタイムシミュレーションが実際に可能かどうかを評価するため、モータの制御を行うリアルタイムシミュレーション環境を構築し、制御試験を行う。図 29 のとおり、MATLAB/Simulink からターゲットPC及びマルチ・ハイスピードデータロガーを経由してモータに制御信号を送信する。制御信号によりモータが駆動するため、この駆動時の回転信号、電流及びモータ温度をそれぞれエンコーダ、電流センサ及び温度センサで測定し、測定結果をマルチ・ハイスピードデータロガー及びターゲットPCを経由して MATLAB/Simulink に送信する。この測定結果をフィードバックしモータの駆動制御を行うことで、マルチ・ハイスピードデータロガーを用いたリアルタイムシミュレーションが可能かどうかを調査する。

### (3) 結果と考察

### ①マルチ・ハイスピードデータロガーを用いたデータ入出力試験

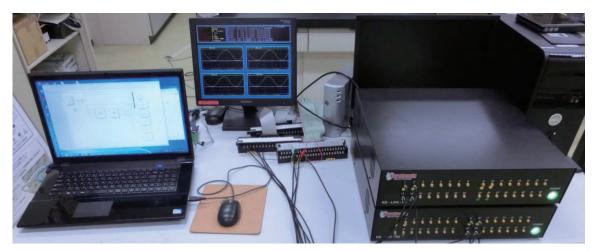

図1に示す試験環境を構築し、マルチ・ハイスピードデータロガーを経由したデータ入出力試験を実施 した。試験環境を図30に、動作確認用モデルを図31に示す。構築した試験環境を用い次のフローで試験 を行う。

⑥入力信号として期間 1 秒, 周波数が 1 秒間に 0.1Hz から 10Hz に変化するチャープ信号を

図29 マルチ・ハイスピードデータロガーを用いたデータ入出力試験

### MATLAB/Simulink 上で作成する。

(ii)入力信号をDA変換ボードから出力し、マルチ・ハイスピードデータロガーを経由してAD変換ボードに出力する。

(iii) AD変換ボードに出力された信号を MATLAB/Simulink 上で計測し、入力信号と出力信号を比較することでマルチ・ハイスピードデータロガーでの信号の遅延や電圧の変化を調査する。

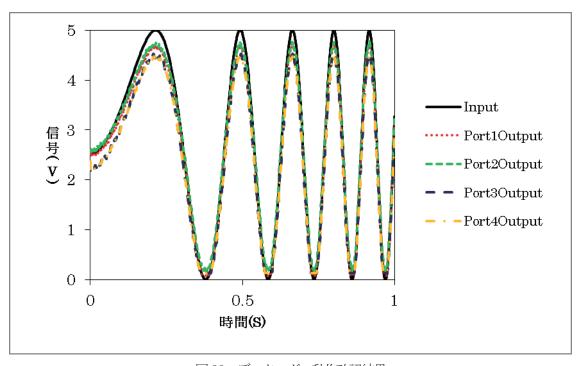

試験結果を図32に示す。図32の結果から、最大値で5Vの入力信号に対し約4.5Vの出力信号しか戻ってきていないことが分かる。これは、試験を行った段階の試作マルチ・ハイスピードデータロガーがまだ調整中であり、信号の入出力のバランスが取れていなかったことが原因である。データの遅延はほぼ見られないため、この電圧降下をシミュレータで補正すれば、試作したマルチ・ハイスピードデータロガーを用いたリアルタイムシミュレーションは問題なく実行可能であるため、出力信号の入力信号に対する減衰割合を測定したところ、マルチ・ハイスピードデータロガーの上部ユニットに当たるPort1、Port2では約93%、マルチ・ハイスピードデータロガーの下部ユニットに当たるPort3、Port4では約89%であった。このことから、Port1、Port2への信号は1.07倍、Port3、Port4への信号は1.12倍に増幅することで本来の信号の値に近似された信号が得られることが分かる。

図30 構築した試験環境

図31 試験用モデル

図32 データロガー動作確認結果

# ②マルチ・ハイスピードデータロガーを経由したリアルタイムシミュレーション試験

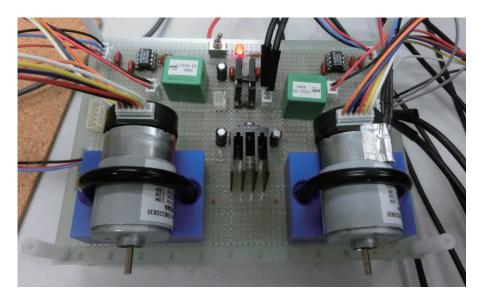

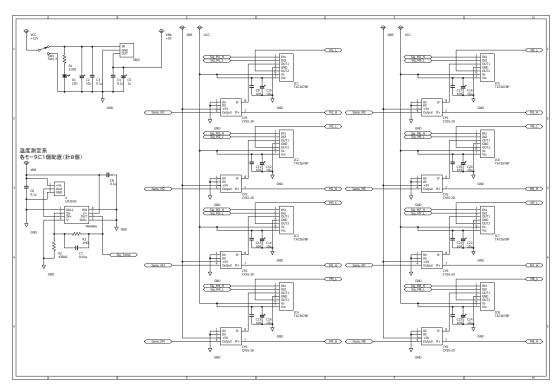

図 29 に示す試験環境を構築し、マルチ・ハイスピードデータロガーを経由したリアルタイムシミュレーション試験を実施した。試験環境を図 33 に、モータドライバを図 34 に、モータドライバの回路図を図 35 に示す。この試験環境を用いてモータ制御を行うため、回転数を目標値に制御する PID 制御によるフィードバック系とモータ駆動電流及びモータ温度が 3A 及び 100℃を超えた場合にモータの駆動を停止させるフィードバック系を備えた図 36 に示すモデルを作成し、このモデルを用いて次のモータ駆動試験を行った。なお、これら試験のサンプリング時間は 0.01 秒、シミュレーション時間は 60 秒である。

### (i)回転数制御をしないモータ駆動試験

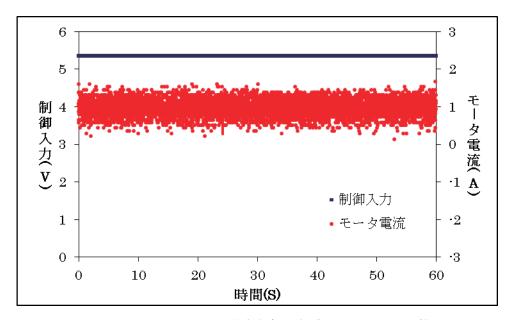

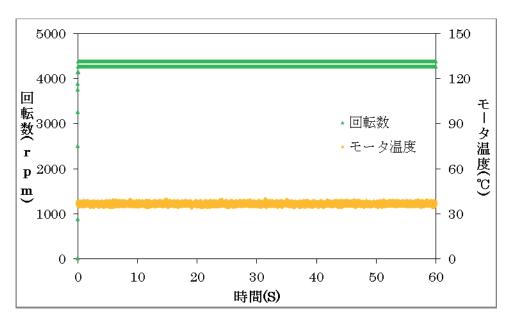

回転数制御を行わない状態でのモータの駆動を確認するため、図 36 のモデルにおいて回転数目標値をモータの無負荷回転数よりも高い 5,000rpm に設定して試験を行った。結果を図10及び図11に示す。結果から、制御を行わない状態ではモータは約4,300rpmで回転し、その際モータに流れる電流は約1A,モータ温度は約35℃であることが分かる。このことから、この試験環境でモータの各種信号が問題なくロギングできていることが確認できた。

#### (ii)回転数目標値を3,000rpm としたモータ制御試験

回転数制御試験を行うため、図36のモデルにおいて目標回転数を3,000rpm に設定して試験を行った。 結果を図39及び図40に示す。結果から、試験開始から終了までの回転数の平均値は3,002rpm であり、 目標の回転数である3,000rpm に制御できていることが分かる。このことから、このシステムでモータの フィードバック制御が行えることが確認できた。

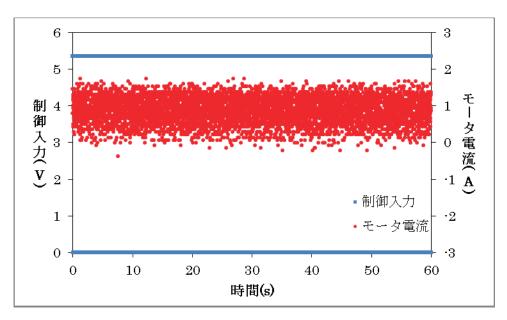

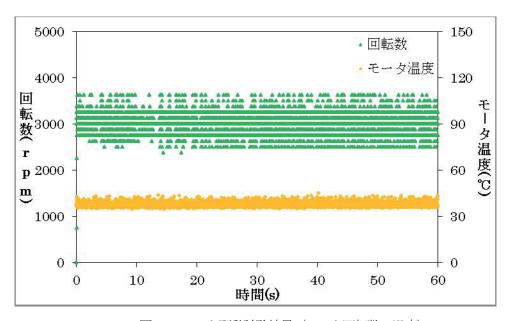

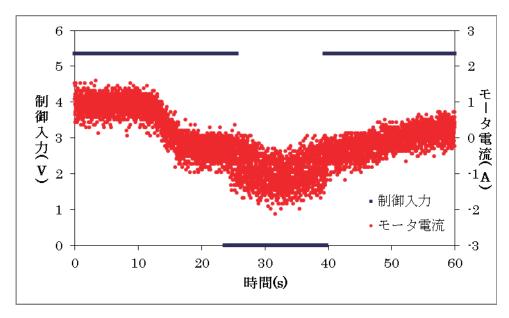

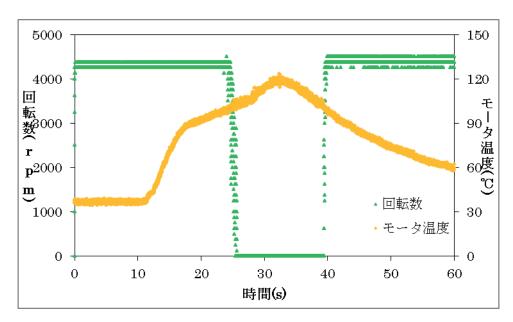

#### (iii)モータの温度制御試験

図36のモデルにおいて、回転数目標値を5,000rpm に設定することで、回転数制御を行わない状態とし、シミュレーション開始から10秒後にヒータにてモータ表面を120℃まで加熱し、モータ温度が120℃まで達した時点でヒータを停止することで、温度によるフィードバック制御が働いているか確認する試験を行った。結果を図41及び図42に示す。結果から、試験開始から約24.2秒後にモータ温度が100℃を超え、100℃を超えた段階でモータを停止させる制御が機能していることが分かる。また。モータ温度が120℃到達後ヒータを停止したところ、試験開始から約39.4秒後にモータ温度が100℃を下回り、モータが駆動を再開したことが分かる。このことから、このシステム温度制御によるモータの起動・停止制御が行えることが確認できた。

①及び②の結果から、試作したマルチ・ハイスピードデータロガーを用いたラピッドコントロールプロトタイピング環境が構築でき、フィードバック制御試験が可能であることが確認できたが、(1)の結果に示すように、出力信号が減衰するなど、実用上の問題があることが判明した。また、今回の試験では、データのロギング機能の実装が間に合わず、データロガーへのデータ保存は行えていない。実用化には、これら問題点の改善が必要である。

図33 試験環境

図34 モータドライバ

図35 モータドライバ回路図

図36 制御モデル

図37 モータ駆動試験結果(制御入力,モータ電流)

図38 モータ駆動試験結果 (モータ回転数,温度)

図39 モータ駆動試験結果(制御入力,モータ電流)

図40 モータ駆動試験結果 (モータ回転数,温度)

図41 モータ駆動試験結果(制御入力,モータ電流)

図 42 モータ駆動試験結果 (モータ回転数, 温度)

この報告書には、委託業務の成果として、産業財産権等の対象となる技術情報(未出願 又は未公開の産業財産権等又は未公開論文)、ノウハウ等の秘匿情報が含まれているので、 通例の取扱いにおいて非公開とする。ただし、行政機関の保有する情報の公開に関する 法律(平成11年法律第42号)に基づく情報開示請求の対象の文書となる。