## 平成25年度戦略的基盤技術高度化支援事業

「微細貫通配線及びバンプ接合を使った次世代三次元 LSI チップ製造技術の確立を 目指した研究開発」

研究開発成果等報告書

平成26年3月

委託者 東北経済産業局 委託先 宮城県中小企業団体中央会

# 目 次

| 第1章 | 研究開発の概要                  | 4   |

|-----|--------------------------|-----|

| 1-1 | 研究開発の背景・研究の目的及び目標        | 4   |

|     | (1)研究開発の背景・目的            | 4   |

|     | (2) 研究の目標                | 10  |

|     | (3)研究実施内容                | 1 1 |

| 1-2 | 研究体制                     | 12  |

|     | (1)研究組織及び管理体制            | 12  |

|     | 1)研究組織                   |     |

|     | 2)管理体制                   |     |

|     | (2) 管理員及び研究員             | 13  |

|     | (3)経理担当者及び業務管理者          | 14  |

|     | (4) 他からの指導・協力者名及び指導・協力事項 | 1 4 |

| 1-3 | 成果概要                     | 15  |

| 1-4 | 当該プロジェクト連絡窓口             | 16  |

|     |                          |     |

| 第2章 | 本論                       | 17  |

| 2-1 | チップズレ防止方法の検討             | 17  |

| 2-1 | -1 研究内容                  | 17  |

| 2-1 | -2 結果                    | 17  |

| 2-2 | ボイド防止構造の検討               | 19  |

| 2-2 | 2-1 研究内容                 | 19  |

| 2-2 | 2-2 結果                   | 19  |

| 2-3 | In/Au バンプ構造・接合の最適化       | 20  |

| 2-3 | 3-1 研究内容                 | 20  |

| 2-3 | 3-2 結果                   | 20  |

| 2-4 | 信頼性技術の開発                 | 23  |

| 2-4 | 1 研究内容                   | 23  |

| 2-4 | 2 結果                     | 23  |

| 2-5 | 事業化に関する研究                | 24  |

| 2-5 | 5-1 顧客開拓                 | 24  |

| 2-5 | 5-2 事業化に向けての市場調査         | 24  |

# 第3章 全体総括

| 3-1 | 平成  | は23-25年度の研究成果の纏め | 25 |

|-----|-----|------------------|----|

| 3-2 | 今後  | その課題             | 26 |

| 3-2 | 2-1 | 三次元 LSI 技術       | 26 |

| 3-2 | 2-2 | 事業化に関する準備と調査     | 26 |

#### 第1章 研究開発の概要

#### 1-1 研究開発の背景・研究目的及び目標

#### (1)研究開発の背景・目的

近年三次元LSIの研究開発が加速している。三次元LSIは小型化、高速化、多機 能化、異種デバイスの集積化、超並列処理可能といった特徴がある。しかし、現行 の技術は貫通配線及びバンプサイズが大き過ぎ、LSI チップ間の回路ブロックを直 接結線ができないためチップ小型化の追求だけでとどまっており、本来の構造的メ リットが有効にでていない。この技術は、LSIウェーハプロセスとアプリケーショ ンを繋ぐ技術であり、研究レベルで多種多様な形成技術が考えられ提案されている が、想定するアプリケーションやウェーハプロセス技術が明確でない場合、ポイン トをはずし無駄な開発をしてしまうことが多い。本研究では、東北マイクロテック 株式会社で研究開発中の高エネルギー物理学で使われるピクセル型素粒子検出器用 LSI を開発ビークルとして、現行のものに比較して 1 桁以下の 2~3 μm で寄生容 量の小さいチップ間接続が行える製品化技術を作ることを目指す。東北マイクロ テック株式会社では、今まで  $5 \mu$ m ピッチ以下の接続技術を研究してきており、そ の試作のための試作装置を開発して、TEG(Test Element Group)チップを試作 して技術検証を行ってきた。しかし、後述するが、大規模回路検証用のテストチッ プで不具合が見つかり、製品化を目指すには単純な TEG を使った研究レベルの開 発から、実製品に近い複雑な配線や断面構造でも積層出来るような製品化技術が必 要であることが分かった。この実製品に繋がる技術を研究するのが本研究の目的で あり、これによって今まで TEG レベルでも他社でできなかった微細貫通配線、マ イクロバンプ接続技術の完成度を上げ、弊社にしか実現できないオンリーワン技術 の実現を目指す。この技術が3年で確立できれば、市場規模が100億円/年の素粒 子検出器用チップのマーケットシェアの大部分が獲得できる。さらには直接の応用 として高速・高機能イメージセンサ、高精度で安価な放射線検出器、医療用のX線 検出器に、その先の超並列型信号処理機能を持つ計算機、超小型の多機能通信モ ジュール、1000 フレーム/秒以上のスピードが必要な高速カメラや 4kx2k (4096×2048) のデジタルシネマ用レンダリング装置、高速移動体のナビ ゲーションシステム用LSIに展開できる。

くじかい型素粒子検出器用 LSI チップを本研究・開発のビークルとして選んだ理由> 現在、三次元 LSI の開発は、イメージセンサの小型化、DRAM やフラッシュに代表されるメモリの高集積化が目標となっている。イメージセンサは30 フレーム/秒、高速といっても300 フレーム/秒で画像データをセンサ領域から出力出来れば良い。画像データは、1 画素ずつ順次出力される。次の画素を出力するピクセルの位置が決まっているので、画像を送り出す準備は、前の画像を送り出す処理サイクル内で準備できる。このように、規則通りに順次データを送るような画像データの高速転送は画素データ間の出力間隔を狭めれば実現できるので、一つのデータに着目するとあまり高速性は必要ない。これは、従来の二次元 LSI で実現可能であり、高速化・高性能化の強い動機にならない。また、DRAM やフラッシュも通常の階層構造のメモリを持つコンピュータシステムでは、下位のメモリ(用語説明欄参照)として使われ、データは上位メモリに、塊として送られるため、これもデータの出力間隔を狭めデータ出力本数を最大100本程度にすれば、ギガ(10°)バイト/秒のデータ転送速度を実現できるので高速化を追求するという意味での強い動機にはならない。

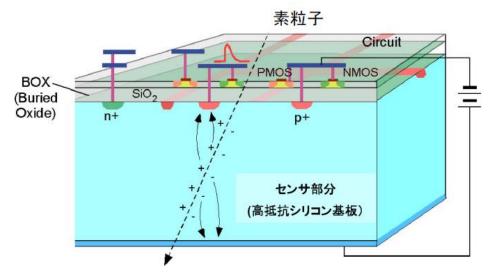

素粒子検出器に使われる検出用LSIは、大型の粒子加速器で粒子(陽子、反陽子等)を加速させて衝突させ、そこで分裂して発生した素粒子の質量、運動エネルギーから素子の性質を推定するための位置、時間を検出する半導体チップである<sup>1</sup>。検出器チップの一例を図 1.1.1 に示す。加速される粒子は 100 個程度のある纏

図 1.1.1 ピクセル型素粒子検出器の一例

5

<sup>1</sup> 新井康夫他, "SO I 技術を用いた放射線イメージセンサの開発",日本物理学会誌 Vol.65, No.9,pp.691-698,2010

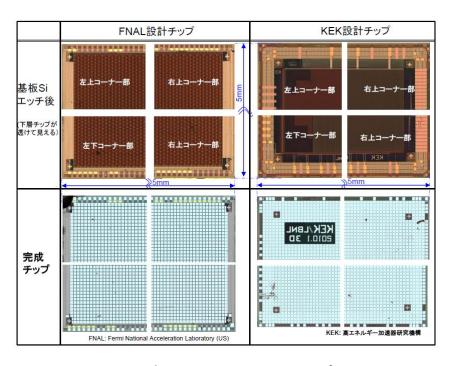

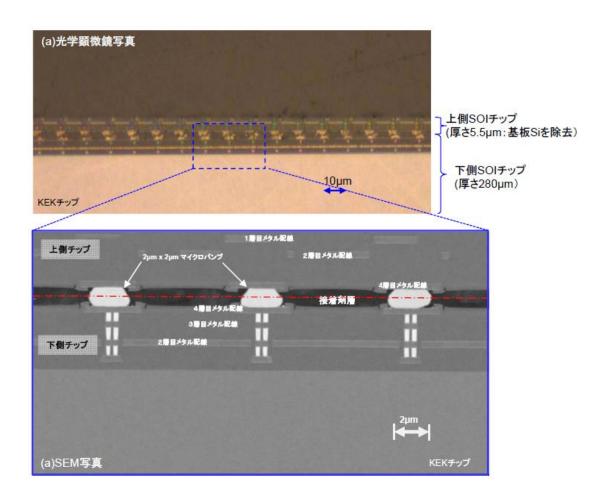

まった量 (bunch)の粒子の衝突が数  $ns(10^{-9}$  秒) の間隔で発生するので、観測 のためにはどの bunch の衝突で発生したか、どの位置を通過したかが分かること が重要である。このため、検出器はピクセル型にする。また、これだけの微少時間 間隔で起こる事象の情報はそのまま外部に送り出しても、高速すぎて処理できない ので、検出器 LSI の内部に、特に高速の事象を扱う場合は 1 ピクセル内に計数回路 を入れる。LSIの内部のうちセンサ部以外は素粒子に対して不感である。高速化の ために計数回路を1ピクセルごとに持たせると更に不感領域が増える。LSIの回路 や配線遅延計数回路の専有面積は数十 μm²になるので、同じピクセル内に入れる と不感領域の割合が半分以上占めることになる。ピクセルサイズを大きくして不感 領域の割合を下げることも考えられるが、空間分解能は下がる。時間分解能と空間 分解能をともに上げるには、検出部分と計数部分を分けて積層し、1 ピクセルごと に両者を電気的に接続することが必要で、このためには 1 ピクセル当たり 1~3 個 の割合でチップ間を接続できるサイズのマイクロバンプ技術が必須になる。弊社は 高エネルギー加速器研究機構(以降 KEK と呼ぶ)及び(米) Fermi National Accelerator Laboratory (以降 FNAL と呼ぶ)の依頼を受けて、SOI(Silicon on Insulator) チップを  $2\mu$  mのマイクロバンプを使って積層する検出器用 LSI チップの 研究をしている。 図 1.1.2 に両機関が設計したチップ写真を、 図 1.1.3 に KEK チップの断面写真を示す。

図 1.1.2 ピクセル型素粒子検出器チップの外観写真

図 1.1.3 KEK のピクセル型素粒子検出器チップの断面写真

ディテクタ試作の依頼この微細マイクロバンプによる接合は、弊社しかアナウンスしていないため、現在はこの他に、(英)Rutherford Appleton Laboratory からサンプル試作受注を受け、試作品を作成した。また、ヨーロッパの核物理関係のAIDA Pj(AIDA: Advanced European Infrastructures for Detectors at Accelerators)から、微細バンプを使ったピクセルが来ており、プロジェクトのメンバの(Pavia University(伊)、Max Planck Institute((独))とピクセルディテクタのレイアウト設計を行っている。但し、弊社は研究用の評価サンプルレベルまでは試作できるが、実装評価に耐える信頼性を持つチップを数百個/月という規模で製造することは、製造装置、工数及び歩留りという点で対応できない。また、弊社で研究用に設計した TEG では問題なかったが、KEK 及び FNAL で設計した大規模回路評価用テストチップでは、今まで見えていなかった問題が露見し、また、ベー

スLSIウェハの製造元が変わるとプロセスチューニングが必要になり製品ごとの開発期間が延び、今持っている技術だけでは直ぐに製品化できないことが分かった。今までは、単純化した TEG デバイスで開発してきたが、本研究で、実際の製品に適用される構造のチップを使い、そこで発生する問題を解決して、インテグレーション(集積化)プロセスを構築することを目的とする。製品レベルのチップで歩留りを上げられ、マージンの大きいプロセス技術が開発できれば、前記の課題が対策され、どこのベース LSI ウェハを使っても 100 個/月レベルのサンプル出荷ができ、素粒子検出器 LSI チップで事業化のスタートが図れる。更にこの技術を必要とする他の製品群に展開でき、ビジネスチャンスを拡大できると考えている。

#### く当該分野における研究開発動向>

前述のとおり、三次元LSI技術を使ったはサンプル出荷・量産ベースでは、今のところ携帯電話のビデオ電話用イメージセンサ用 CSP(チップサイズパッケージ)と 積層 DRAM、一部の Si インターポーザに搭載された FPGA(2.5D 技術)しかない。開発フェーズでは、通信モジュールで Qualcom(米)社が企画、IMEC(ベルギー)の開発技術で SMC(台湾)が製造というスキームの共同開発を行っている例がある。また厳密にいうと三次元LSI ではないが Xilinx 社の次世代の FPGA は 4 チップに分割され、Si インターポーザ上に積層される。これは、製品化初期の歩留り低によるコストアップを避けるためである。これらの技術で使う TSV,バンプサイズは、それぞれ 10μm 径及び 30μm 径以上である。この他に、IBM 社はスーパーコンピュータ用に独自のウェーハプロセスで積層する三次元積層技術を開発中であるが、この方法ではコスト的にコンシューマ向けに大量生産するデバイスカテゴリには高価で不向きである。

研究レベルでは、世界各国の研究機関が各社各様の技術を開発している。これを表 1.1.1 に纏めた。弊社及び東北大、IMEC (ベルギー), CEA-LETI(仏), Fraunhofer(独), Tezzaron (米) は $5\mu$ m径以下のTSVを発表している。バンプサイズは、弊社及び(米) Ziptronix 社の $2\mu$ m径以外は、 $5\mu$ m以上である。

表 1.1.1 各社が発表している三次元 LSI 技術

| TSV形成工程          |                        | 1                                                   | 表□ 4台 II 4 元十十六                                                       | LS <b>Iウェー</b> ハプ<br>積層前                                                 |                                | プロセス | 田廷ユノディ          |

|------------------|------------------------|-----------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------|------|-----------------|

| /                | ZSV.                   | MOS形成前                                              | 日C和永万夕八月月                                                             | tg/音印<br>TSV形成                                                           | 積層後<br>TSV形成                   | コスト  | 異種サイズ/<br>基板の積層 |

| 積層方              | ISV <sub>村料</sub><br>法 | ポリシリコン                                              | Cu, W                                                                 | W, Cu                                                                    | W, Cu                          |      |                 |

| ウェハ<br>状態で<br>積層 | バルク<br>Si              | 東北大<br>IBM<br>Dalsa                                 | Tezzaron<br>Ziptronix<br>IMEC<br>TSMC<br>ASET<br>エルピーダ<br>三星<br>Hynix | 東北大<br>CEA-LETI<br>IMEC<br>Toshiba<br>ASET<br>Samsung<br>STMicro<br>Etc. | Samsung<br>(開発)                | 低    | 不可              |

|                  | SOI                    |                                                     |                                                                       | 東北大                                                                      | IBM<br>RPI<br>MIT/Lincoln Lab. |      |                 |

| ウェハ上に<br>チップを積層  |                        | 東北大.                                                |                                                                       | Frounhofer IZM<br>Samsung<br>CEA-LETI<br>Ziptronix<br>IMEC               |                                | 中    | 可能              |

| *自己組織化<br>技術     |                        |                                                     |                                                                       | *東北大<br>(東北マイクロテック)                                                      |                                | *低   |                 |

| チップ状態<br>で積層     |                        | <ul><li>東北大</li><li>・エルピーダ</li><li>(初期開発)</li></ul> |                                                                       | ・東北大<br>(東北マイクロテック)<br>・RTI                                              |                                | 高    | 可能              |

バルクSi : 基板全体がSiで構成(通常のLSIで使われるSi基板) SOI (Silicon on Insulator): 絶縁膜上に薄いSiのデバイス層が形成されている基板 弊社は In/Au の溶融接合方式である。この実現のため、チップアライメント、接着剤注入、接着剤硬化専用装置も含めて研究開発することで実現することができ差異化が図れている(図 1.1.5)。

図 1.1.5 マイクロバンプ接合用装置

#### (2)研究の目標

目標は、現行のプロセスの問題点・課題を改善して、実使用に耐えうる信頼性・歩留りを確保できる三次元 LSI チップ製造技術を開発することである。

- 積層チップの仮接着後にチップがずれないようにズレ防止構造を検討する。

【技術目標】 仮接着後から恒久接着までの間にチップずれを起こさないこと。

- 2. 接着剤注入時にボイドが入らない構造・プロセスを構築する。

#### 【技術目標】

Si エッチ後、20 倍の対物レンズの光学顕微鏡(接眼レンズ 10 倍)で観察してボイドが無いこと。

3. 2.5 μmx2.5 μm の ln/Au マイクロバンプ接合でバリア/コンタクトメタルの選定を行い TEG チップ、回路 TEG チップで安定なバンプ抵抗を得ること。また、 ln/Au が下地のデバイス領域に拡散しない様なバリアメタルを選択すること。

#### 【技術目標】

- ・加熱温度プロファイルの最適化後、信頼性試験での接合不良率が 0.01% 以下であること

- 高温放置後でバンプ/バンプパッドメタルから下地 MOS トランジスタ領域への Au の拡散が分析器 (SIMS) の検出限界以下であること。

- 4. 以下の信頼性試験を満足すること

#### 【技術目標】

- 1000 段以上の Daisy Chain の温度サイクル試験で500サイクルまでで導通 不良が発生しないこと。不良が発生した場合は、原因対策を行い、不良が発生し ないという見通しを得ること。

- ・エレクトロマイグレーション試験で、0.3 x 10<sup>5</sup>A/cm<sup>2</sup>が実現できること。

#### (3)研究実施内容

| 研究項目                         | 目標                                                                                                                                                                               | 実施結果                                                                                                                                           |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| ①チップズレ防止方法の検討                | <ul><li>仮接着後から恒久接着までの間に<br/>チップずれを起こさないこと。</li></ul>                                                                                                                             | ズレ発生メカニズムを解明し、三次<br>元積層装置及び積層プロセスを最適<br>化した。                                                                                                   |

| ②ボイド防止構造<br>の検討              | • 20 倍の対物レンズの光学顕微鏡<br>(接眼レンズ 10 倍)で観察して<br>ボイドが無いこと。                                                                                                                             | 接着剤注入プロセス及びレイアウトパターンの最適化を行いSOIウェハを使った専用TEGを設計・試作しボイド有無を観察した。                                                                                   |

| ③In/Au バンプ構造<br>の最適化         | <ul><li>接合不良率が 0.01%以下であること</li><li>バンプメタルの下地への拡散が分析器 (SIMS) の検出限界以下であること</li></ul>                                                                                              | バンプ形成プロセスの見直し、バンプ組成、バリアメタルの最適化により、安定的にバンプ抵抗が得られることを確認した。また、Auの下地への拡散の評価用TEGを作成・評価を行い、SIMS分析で確認した。                                              |

| ④/言頼性評価試験                    | <ul> <li>1000 段以上の Daisy Chain の<br/>温度サイクル試験で 500 サイク<br/>ルまでで導通不良が発生しないこ<br/>と。</li> <li>バンプ EM 試験で、最大電流密度<br/>0.3 × 10<sup>5</sup>A/cm<sup>2</sup>以上が実現で<br/>きること。</li> </ul> | 信頼性評価用 TEG チップを設計し、最適化したプロセスで試作し、セラミックパッケージに組み込み温度サイクル試験を行った。<br>EM 試験はウェハ状態で定電流ストレスを印加し評価した。                                                  |

| ⑤事業化に関する<br>準備と調査            | ・現在協力関係にある高エネルギー加速器研究機構を通して素粒子検出器市場を、また、新たな高機能センサ等の市場及び医療用・高速コンピュータ用プロトタイプ3DIC市場を開拓する。これは、3年間を通して活動する。 ・最先端の三次元LSIの学会参加し最新の技術を調査し、本開発技術とベンチマークを行う。                               | 【顧客開拓】<br>平成24年度は2つの国内の展示会に出展、平成25年度は7つの国内外の展示会に出展し顧客開拓を図った。<br>【市場調査・学会での情報収集】<br>平成23~25年度を通して、主要な三次元LSIのでの発表・参加し、技術動向調査、他社・他機関とのベンチマークを行った。 |

| ⑥研究全体の統括、<br>プロジェクトの管理運<br>営 | <ul><li>研究を円滑に推進するため、一連の研究全体について管理運営を統括する。</li><li>また、事業の進捗についての確認を定期的に行い、適正な管理を行う。</li></ul>                                                                                    | 一連の研究全体について管理運営<br>を統括し、事業の進捗についての<br>確認を定期的に行い、研究を円滑<br>に推進した。                                                                                |

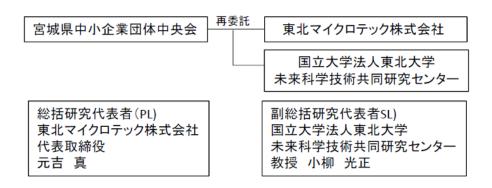

#### 1-2 研究体制

#### (1)研究組織及び管理体制

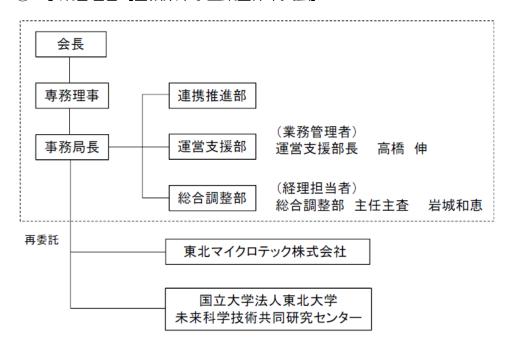

1)研究組織(全体)

#### 2)管理体制

① 事業管理者 [宮城県中小企業団体中央会]

#### ② (再委託先)

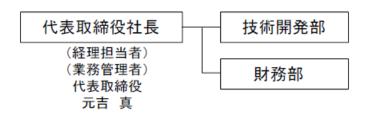

東北マイクロテック株式会社

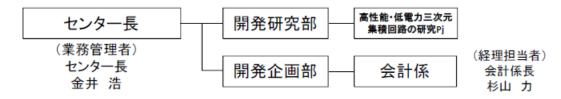

#### 東北大学未来科学技術共同研究センター

#### (2) 管理員及び研究員(役職・実施内容別担当)

#### 【事業管理者】宮城県中小企業団体中央会

#### 1)管理員

| 氏名    | 所属•役職            | 実施内容<br>(番号) |

|-------|------------------|--------------|

| 高橋 伸  | 運営支援部 部長         | 6            |

| 佐野 智之 | 運営支援部軍営支援第二課課長   | 6            |

| 佐藤 一三 | 運営支援部運営支援第二課主任主査 | 6            |

## 【再委託先(研究員)】

## 東北マイクロテック株式会社

| 氏名     | 所属•役職     | 実施内容<br>(番号) |  |

|--------|-----------|--------------|--|

| 元吉 真   | 代表取締役     | PL:1,2,3,4,5 |  |

| 長谷川 峰司 | 設計部長(研究員) | 5            |  |

| 鷹觜 淳一  | エンジニア     | 1,2,3,4      |  |

| 佐竹 伸   | エンジニア     | 1,2,3,       |  |

| 伏見 泰広  | 補助員       | 1,2,3,       |  |

| 柳村光紀   | 補助員       | 1,2,3,4      |  |

#### 国立大学法人東北大学未来科学技術共同研究センター

| 氏名           | 役職•所属               | 実施内容<br>(番号) |

|--------------|---------------------|--------------|

| 小柳 光正        | 未来科学技術共同研究センタ- 教授   | SL:1,2,3,4,5 |

| 李 康旭         | 未来科学技術共同研究センタ- 教授   | 1,2,3,5      |

| 福島 誉史        | 未来科学技術共同研究センター准教授   | 1,2,3,5      |

| Jichoel Bea  | 未来科学技術共同研究センタ- 助教   | 1,2,3        |

| M. Murugesan | 未来科学技術共同研究センター研究員   | 3,4,5        |

| 相沢宏行         | 未来科学技術共同研究センター研究補助員 | 1,2          |

| 長井・千里        | 未来科学技術共同研究化外一研究補助員  | 1,2          |

#### (3) 経理担当者及び業務管理者

#### 【事業管理者】

宮城県中小企業団体中央会

(経理担当者)総合調整部 主任主査 岩城 和恵

(業務管理者) 運営支援部 部長 高橋 伸

#### 【再委託先】

東北マイクロテック株式会社

(経理担当者) 代表取締役 元吉 真

(業務管理者) 代表取締役 元吉 真

国立大学法人東北大学未来科学技術共同研究センター

(経理担当者) 会計係長 杉山 力

(業務管理者) センター長 金井 浩

# (4) 他からの指導・協力者名及び指導・協力事項研究推進会議 委員

| 氏名 |    | 所属•役職                      | 備考     |

|----|----|----------------------------|--------|

| 元吉 | 真  | 東北マイクロテック株式会社(代表取締役)       | PL 孁   |

| 小柳 | 光正 | 国立大学法人東北大学未来科学技術共同研究センター教授 | SL     |

| 田中 | 徹  | 国立大学法人東北大学医工学研究科教授         | アドバイザー |

| 新井 | 康夫 | 高エネルギー加速器研究機構 素粒子原子核研究所 教授 | アドバイザー |

| アドバイザー | 主な指導・協力事項              |

|--------|------------------------|

| 氏 名    |                        |

| 田中徹    | 三次元 LSI 用プロセス装置使用方法助言  |

| 荒井 康夫  | ピクセルディテクタの設計、指導、評価及び助言 |

# 1-3 成果概要

表2に研究成果概要を纏める。

# 表2 成果概要

| 研究開発目標                   | 研究開発成果                                                                                                                                                                                                           |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ①チップズレ防止方法の 検討           | ズレ発生メカニズムを解明し、三次元積層装置及び積層プロセスを最適化した。これによりマニュアル合せであるが2.5 μ x 2.5 μm マイクロバンプ TEG で 溶融後、ほぼ 100%の接合面積が得られた。                                                                                                          |

| ②ボイド防止構造の検討              | 注入プロセス及びレイアウトパターンの最適化を行い専用 TEG を設計・試作しボイドを防げることを確認した。                                                                                                                                                            |

| ③In/Au バンプ構造の最<br>適化     | バンプ形成プロセス途中で形成されるメタル酸化膜の影響をなくしさらに、バンプ組成、バリアメタルの最適化により、安定的にバンプ抵抗が得られることを確認した。また、Auの下地への拡散の評価用 TEG を作成・評価を行い、SIMS 分析により Auの濃度が検出限界以下であることを確認した                                                                     |

| ④信頼性評価試験                 | 平成24年度に設計した TEG チップを試作し、温度サイクル試験と EM(Electromigration) 試験をおこなった。温度サイクル試験(-45℃⇔150℃) では、目標の500サイクルまで評価し、導通不良の発生は見られなかった。EM評価は、目標の電流密度 3.0 x 10 <sup>4</sup> A/cm <sup>2</sup> 以上をクリアすることができた。                     |

| ⑤事業化に関する準備と調査            | 【顧客開拓】 平成24年度は国内の2つの展示会に出展、平成25年度は7つの国内外の展示会に出展し顧客開拓を図った。技術の問い合わせ件数受注数も平成24年度に対し平成25年度は10倍以上増加した。 【市場調査・学会での情報収集】 平成23~25年度を通して、主要な三次元LSIの学会に参加・発表し、技術動向調査、他社・他機関とのベンチマークを行い、世界的な技術動向に沿っていること、技術的な優位性があることを確認した。 |

| ⑥研究全体の統括、プロ<br>ジェクトの管理運営 | 一連の研究全体について管理運営を統括し、事業の進捗についての確認を定期的に行い、研究を円滑に推進した。                                                                                                                                                              |

#### 1-4 当該プロジェクト連絡窓口

宮城県中小企業団体中央会

TEL:022-000-5560 FAX:022-222-5557

総括責任者 高橋 伸 m10shint427@chuokai-miyagi.or.jp

東北マイクロテック株式会社

TEL: 022-398-6264 FAX: 022-398-6265

統括責任者 元吉 真 motoyoshi@t-mictotec.com

国立大学法人 東北大学 未来科学技術共同研究センター

TEL:022-759-6906 FAX:022-795-6907

統括責任者 小柳 光正 koyanagi@bmi.niche.tohoku.ac.jp

#### 第2章 本論

#### 【研究内容・及び成果】

#### 2-1 チップズレ防止方法の検討

#### 2-1-1 研究内容

三次元 LSI の積層の段階で、チップアライメント・仮接着後から恒久接着の間にチップ ずれが起こり、アライメント時の合わせ精度が完成時に得られていないという問題があっ た。この対策のため、チップズレ評価用の TEG 設計を行い、これを用いてズレ防止構造 の有効性について検証する。

#### 2-2-2 結果

#### (1) 合わせズレ対策効果の確認

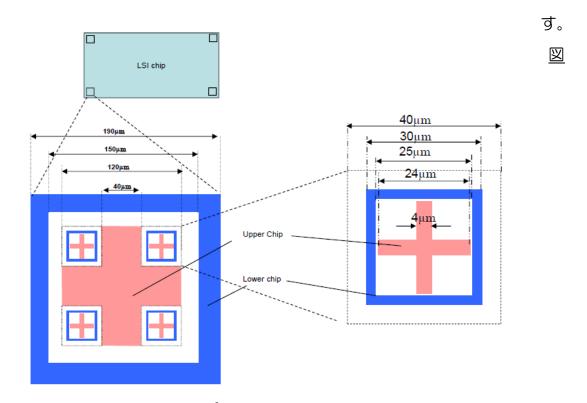

図 2.1.1 にチップアライメントマークレイアウトとチップ内の配置図を示

2.1.1 チップアライメントマークのレイアウト

青いパターンは下部チップ、赤いパターンは上部チップの最上層メタルで形成してあり、チップの下から赤外光を入れ上から赤外線顕微鏡観察しながらアライメントする。マークはチップの大体の位置を合わせる(ショット位置を合わせる)190μmロのマーク(rough alignment mark)とこの内部にレイアウトした30μmロの4つのアライメントマーク(fine alignment mark)からなる。十字マークは上側

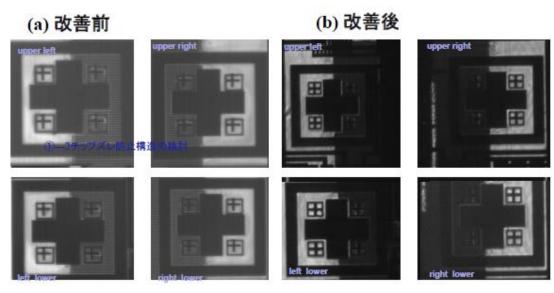

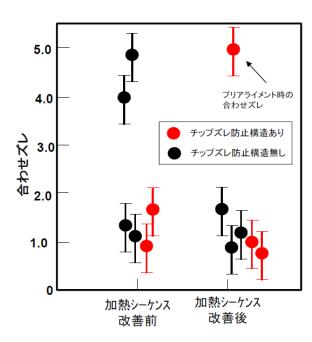

チップにボックスマークは下側チップに形成されており、合わせずれが無い状態では赤外線顕微鏡でみるとボックスの中の十字マークが中央に配置されているように見える。 対策は、バンプ接合及び接着時の温度プロファイルいの最適化及びズレ防止用パターンを入れておこなった。図 2.1.2 にプロセス及び構造の改善前後の積層チップのアライメントマークを示す。画像は積層チップ裏から赤外線を当て赤外線顕微鏡により取得した。 改善後はプリアライメントから殆ど位置がずれていないことが分かる。

図2.1.2 プロセス改善前後のチップアライメントマーク

この結果を図2.1.3 に纏めた。

アライメント装置の改造により、プリアライメントの精度が 2μm 以下に向上したが図のようにプリアライメント時に合わせずれが 2μm 以下の場合、仮接着から恒久接着までの間にチップずれがさらに大きくなるということはなくなった。 In 半田バンプの場合は、溶融して接合するため、2.5μmx2.5μm のサイズのバンプで合わせズレが2μm 以下であればほぼ100%の接合面積が得られる。

図 2.1.3 チップ合わせズレ

#### 2-2ボイド防止構造の検討

#### 2-2-1 研究内容

ボイド発生防止対策は、(1)接着剤注入方法の最適化(2)チップ間の空隙を広げて圧力変動の変化率を下げること(3)局所的な空隙サイズ分布を抑えることの三つが考えられる。これらのパラメタを最適化することによりボイドの発生を抑制する。

#### 2-2-2 結果

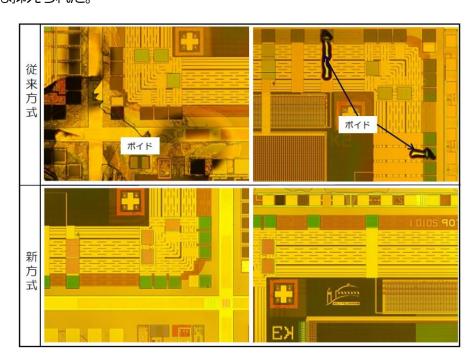

接着剤は、チップ内部の空気を押し出しながら、毛細管現象とチップ内部と外部の差圧により注入される。この二つがバランスし、注入される接着剤の先端が進行方向に対して法線上に入っていくのが理想である。これが大きく崩れるとボイドが発生する。従来は積層チップをほぼ水平に保ち横方向から樹脂を注入していた。チップ間隔が狭く毛細管現象と加圧による効果複雑に入り、チップ表面の凹凸パターンによって接着剤の侵入速度が変わり、回り込むことでボイドが発生した。対策として、チップ間隔を広げるようにバンプを形成し毛細管現象の効果を下げ、樹脂槽に定速でチップ浸漬していく方式に変更した。実験・評価は SOI 積層チップを使い、積層後に上部チップのバルクSi を除去し20倍の対物レンズの光学顕微鏡(接眼レンズ 10倍)でボイドの発生の有無を観察した。従来方式と新方式を図2.2.1 で比較した。この対策により、ボイドの発生は抑えられた。

図 2.2.1 接着剤注入プロセスの最適化前後でのボイドの発生状況

#### 2-3 In/Au バンプ構造・接合の最適化

#### 2-3-1 研究内容

$2.5\,\mu$ mx $2.5\,\mu$ m の  $\ln$ Au マイクロバンプ接合で TEG チップ、回路 TEG チップで安定なバンプ抵抗を得るためバンプ形成プロセスの最適化及びバリア/コンタクトメタルの選定を行う。また、選定したバリアメタルでバンプ材料である  $\ln$ Au が下地のデバイス領域に拡散しないことを SIMS (Secondary Ion Mass Spectrometry) 分析によって確認する。

#### 2-3-2 結果

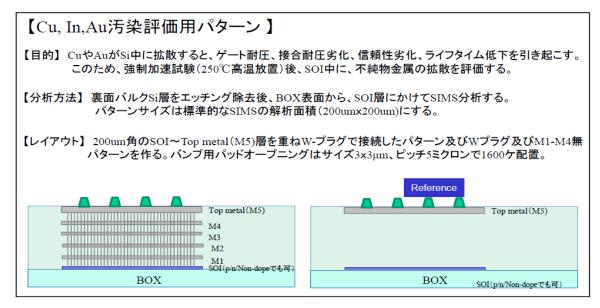

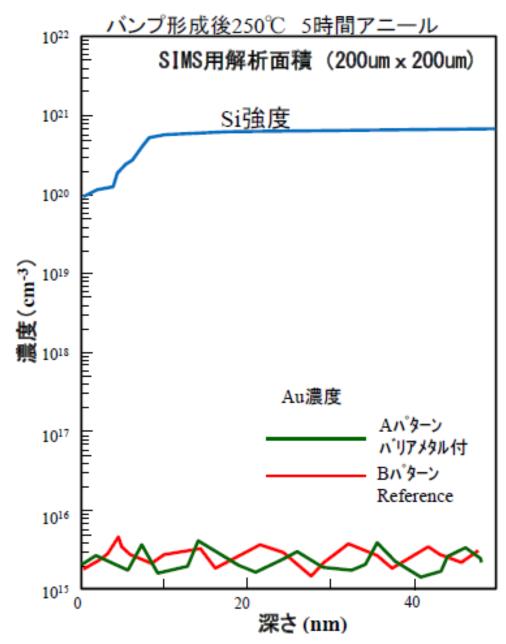

#### (1) バリア性評価

図 2.3.1 にメタル汚染評価用の TEG の断面構造を示す。分析領域は SIMS で十分 な信号が得られるように  $200\,\mu\text{m}$  とした。SOILSI に  $\ln/\text{Au}$  バンプを形成 した後、 $250^\circ$ C 5時間熱処理を行い、配線、層間絶縁膜を除去して SOI 薄膜を出し この部分の不純物分析を行う。リファレンスとして層間膜だけ形成したものを用意した。

図2.3.1 分析用 TEG の断面構造

図 2.3.2 に SIMS 深さ分析結果を示す。 Au の濃度はリファレンスのBパターンと有意差が無いことから、In バンプ表面の酸化防止用の Au の下地への拡散は検出限界以下で無視できると考えられる。

図2.3.2 メタル汚染評価TEGを使ったSIMS分析結果

#### (2)バンプ接合評価

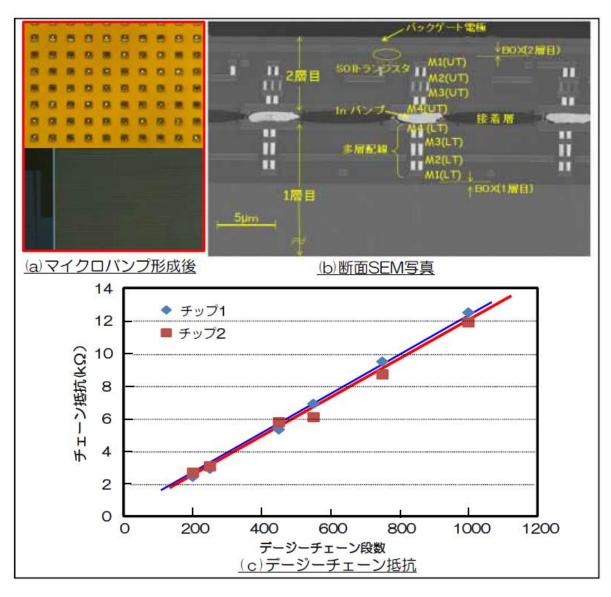

本研究開発で最適化したマイクロバンプを使い、ピクセルディテクタチップを試作した。この結果を図 2.3.3 に示す。搭載されているデージーチェーン TEG の測定結果を図(c)に示す。この TEG には、5 つのタップが出ているがこれらの測定点がほぼ同一線上にならんでいるため、安定した抵抗が取れていると考える。

図2.3.3 ピクセルディテクタチップでの検証結果

#### 2-4信頼性技術の開発

#### 2-4-1 研究内容

バンプ接合部の温度サイクル試験及び EM(Electromigration)試験により、本技術の実用性評価を行った。

温度サイクル試験では、セラミックパッケージに入れて評価するため、京セラの40 品 DIP セラミックパッケージ (KD-80218-C)に搭載できるようなサイズに TEG を設計し、ボンディングパッドもパッケージのパッドと最短距離でワイヤボンドできるように設計した。

#### 2-4-2 結果

#### (1) 温度サイクル試験

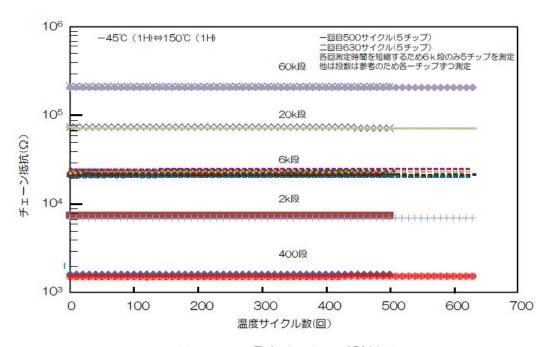

温度サイクル試験は、半導体の標準の温度サイクル条件(-45℃ + 150°C)で行い、500サイクルで不良が発生しないことが目標である。評価結果を図 2.4.1 に示す。

評価では特に不安定な抵抗値を示すものはなく、温度サイクル試験での目標はクリアできた。

図 2.4.1 温度サイクル試験結果

#### (2) EM 試験

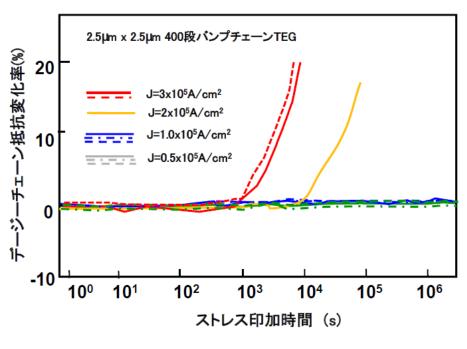

EM 試験の評価は 400 段のデージーチェーンを使った。評価結果を図 2.4.2 に示す。 電流密度 1.0x10<sup>5</sup> A/cm<sup>2</sup> でほとんど変動がみられなかった。この値は大口径バンプ で評価した以前の結果より大きく、微細化したことによりバンプ自体の体積に対して表面積の割合が増えたため、放熱効果が大きくなり許容電流密度が上がったと考えられる。

図 2.4.2 EM 試験結果

#### 2-5事業化に関する研究

#### 2-5-1 顧客開拓

平成 24 年度は国内の 2 つの展示会に出展、平成 25 年度は 7 つの国内外の展示会に出展し顧客開拓を図った。技術の問い合わせ件数受注数も平成 24 年度に対し平成 25 年度は 10 倍以上増加した。以下は平成 2 5 年度に出展した展示会である。

- AIDA-Pi@□-マ (4/8-9)

- 中小企業総合展@大阪(5/23-31)

- •3D SIC@サンフランシスコ(10/1-4)

- ・セミコン2013@幕張メッセ(12/4-6)

- 3D ASIP@サンフランシスコ(12/12-14)

- インターネプコン@東京ビッグサイト(1/15-17)

- 中部もの作り基盤技術展@名古屋(2/8-19)

#### 2-5-2 事業化に向けての市場調査

平成 23~25 年度を通して、主要な三次元 LSI の学会に参加・発表し、技術動向調査、他社・他機関とのベンチマークを行い、世界的な技術動向に沿っていること、技術的な優位性があることを確認した。以下は平成 25年度に参加・発表した三次元関連の学会である

ESTC2014, ECTC2013, 3D-SIC, IEDM2013, ISSCC 2014

# 第3章 全体総括

## 3-1 平成 23-25年度の研究成果の纏め

成果を表3.1 まとめる。

表3.1 平成23-25年度の研究成果の纏め

| 研究開発目標                       | 研究開発成果                                                                                                                                                                                                            | 達成率  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| ①チップズレ防止<br>方法の検討            | ズレ発生メカニズムを解明し、三次元積層装置及び積層<br>層<br>プロセスを最適化した。これによりマニュアル合せであるが2.5 μ x 2.5 μm マイクロバンプ TEG で溶融後、ほぼ 100%の接合面積が得られた。                                                                                                   | 100% |

| ②ボイド防止構造の検討                  | 注入プロセス及びレイアウトパターンの最適化を<br>行<br>い専用 TEG を設計・試作・検証し、ボイド無き<br>ことを確認した。                                                                                                                                               | 100% |

| ③In/Au バンプ構<br>造の最適化         | バンプ形成プロセス途中で形成されるメタル酸化膜の<br>影響をなくしさらに、バンプ組成、バリアメタルの最<br>適化により、安定的にバンプ抵抗が得られることを確<br>認した。<br>また、Auの下地への拡散の評価用 TEG を作成・評<br>価を行い、SIMS 分析により Au が検出レベル以下で<br>あることを確認した                                               | 100% |

| ④/言頼性評価試験                    | 平成24年度に設計した TEG チップを試作し、<br>温度サイクル試験と EM (Electromigration) 試<br>験をおこなった。温度サイクル試験 (-45℃⇔<br>150℃) では、目標の500サイクルまで評価<br>し、導通不良の発生は見られなかった。EM 評価<br>は、目標の電流密度 3.0 x 10 <sup>4</sup> A/cm <sup>2</sup> 以上をクリ<br>アした。 | 100% |

| ⑤事業化に関する 準備と調査               | 【顧客開拓】 平成24年度は2つの展示会に出展、平成25年度は7つの国内外の展示会に出展し顧客開拓を図った。技術の問い合わせ件数受注数も平成24年度に対し平成25年度は10倍以上増加した。 【市場調査・学会での情報収集】 平成23~25年度を通して、主要な三次元LSIの学会に参加・発表し、、技術動向調査、他社・他機関とのベンチマークを行い、開発方向のズレや技術レベルが劣っていないことを確認した。           | 100% |

| ⑥研究全体の統<br>括、プロジェクト<br>の管理運営 | 一連の研究全体について管理運営を統括し、事業の進<br>捗についての確認を定期的に行い、研究を円滑に推進<br>した。                                                                                                                                                       | 100% |

#### 3-2 今後の課題

#### 3-2-1 三次元 LSI 技術

本研究開発により、当初の目標は達成した。今後はディテクタ、X線センサ、赤外線センサの試作に本研究開発で得られた技術を適用していき、インテグレーション技術の完成度を確認していく。また同時に、更なるバンプ TSV ピッチの縮小を並行して検討していく。

#### 3-2-2 事業化に関する準備と調査

顧客開拓に関して今までは技術的な学会や展示会に出展してきた。顧客獲得という意味で成果はあったが、三次元LSI技術は、システムLSIよりの技術であるため、川下企業(エンドカスタマー)と接触ができるような展示会や学会等に向けてかじ取りを修正していき、付加価値の高いデザインインのサンプル試作受注に注力していく。 ピクセル型ディテクタ市場は2016年から伸びていくと推定している。このため、2015年度中に月産数百個レベルの少量量産ができるように生産フロー、ビジネスフロー等の整備を行い対応できるように準備する。