# 平成25年度戦略的基盤技術高度化支援事業

# 「ミニマル 3 次元積層 LSI デバイス製造ファブ に対応したデバイス検査装置の開発」

# 研究成果等報告書

平成26年3月

委託者 九州経済産業局

委託先 一般財団法人 九州産業技術センター

# 目 次

| 第1章 研究開発の概要                 | • | ٠ | • | • | • | • | • | • | 4  |

|-----------------------------|---|---|---|---|---|---|---|---|----|

| 1-1 研究開発の背景・研究目的及び目標        |   |   |   |   |   |   |   |   | 4  |

| 1-2 研究体制                    |   | • | • | • | • | • | • | • | 8  |

| 1-3 成果概要                    |   | • | • | • | • | • | • | • | 13 |

| 1-4 当該研究開発の連絡窓口             | • | • | • | • | • | • | • | • | 14 |

| 第2章 本論                      |   |   |   |   |   |   |   |   | 15 |

| 2-1 デバイス検査装置計測部の開発          |   |   |   |   |   |   |   |   | 15 |

| 2-1-1 デバイス検査装置計測部の設計        |   | • | • | • | • | • | • | • | 15 |

| 2-1-2 デバイス検査装置計測部の試作        | • | • | • | • | • | • | • | • | 17 |

| 2-1-3 デバイス検査装置計測部の基本特性評価    | • | • | • | • | • | • | • | • | 19 |

| (a)プローブ接触抵抗の評価              | • | • | • | • | • | • | • | • | 19 |

| (b) フラッシュメモリによる評価           | • | • | • | • | • | • | • | • | 21 |

| (c) シリコン貫通電極つき 3 次元積層チップの評価 | • | • | • | • | • | • | • | • | 24 |

| 2-2 デバイス検査装置プローブ部の開発        |   |   |   |   |   |   |   |   | 26 |

| 2-2-1 デバイス検査装置プローブ部の設計      | • | • | ٠ | • | ٠ | • | • | • | 26 |

| 2-2-2 デバイス検査装置プローブ部の試作      | • | • | ٠ | • | ٠ | • | • | • | 26 |

| 2-2-3 デバイス検査装置プローブ部の基本特性評価  | • | • | • | • | • | • | • | • | 28 |

| 2-3 デバイス検査装置の統合化            |   |   |   |   |   |   |   |   | 30 |

| 2-3-1 デバイス検査装置の統合化モデルの設計    |   | • |   |   |   | • | • | • | 30 |

| 2-3-2 デバイス検査装置の統合化モデルの試作    |   | • | • | • | • | • | • | • | 30 |

| 2-3-3 デバイス検査装置の統合化モデルの総合評価  | • | • | • | • | • | • | • | • | 31 |

| 第3章 全体総括                    |   |   |   |   |   |   |   |   | 33 |

| 3-1 本研究開発で得られた成果            |   |   |   |   |   |   |   |   | 33 |

| 3-2 事業化への取り組み               |   |   |   |   |   |   |   |   | 34 |

# 第1章 研究開発の概要

#### 1-1 研究開発の背景・研究目的及び目標

#### (1) 背景

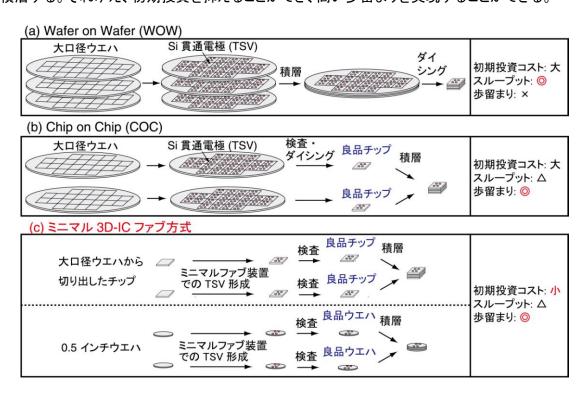

近年、3 次元集積回路 (Three Dimensional Integrated Circuit: 3D-IC)は、集積回路の微細化 に代わる電子システムの高度化手法の一つとして着目されている。これは、集積回路の表面から裏面に 貫通する電極 (シリコン貫通電極、Though Silicon Via: TSV)を形成したものを複数用意して、それら を微細バンプ接続により縦方向に積層して高度な電子システムを実現する技術である。この技術では、縦 方向の配線が可能となるため、従来の 2 次元集積回路技術に比べて配線の自由度が増し、システム全 体の配線長を大幅に短くすることができる。それ故に、①従来の LSI で長い距離の信号伝送に要してい た信号復元回路の削減により消費電力を大幅に低減させることができる。また、②従来のシステムオン チップ (SOC)技術で利用できるオンチップバス配線のビット幅に比べて非常に大きなバス幅を利用できる ため、システムクロック周波数を上昇させることなく並列処理アーキテクチャーの採用によりトータルの信 号処理能力を向上させることが可能となる等の特徴を有する。この 3 次元集積回路を作製する手法とし ては、これまでに WOW (Wafer on Wafer) (図 1-1-1(a))、COC (Chip on Chip)(図 1-1-1(b))など が提案されている。WOW の場合には、200/300 mm 集積回路形成済みウエハに対して、TSV や微細 バンプを形成し、ウエハのまま積層を行う、というものである。この方法では、ウエハのまま積層するため に、スループットが格段に高い。一方で、200/300 mm 対応の大規模プロセス装置の購入・運用が必要 となり、開発コストが膨大になるとともに、不良チップをそのまま積層するために歩留まりが低い。COC の 場合には、200/300 mm 集積回路形成済みウエハに対して、TSV や微細バンプを形成した後で、検査・ 個片化を行い、良品チップと不良チップの分別を行い、良品チップを積層する。この方法では、歩留まりは 高くなるが、200/300 mm 対応の大規模プロセス装置の購入・運用のために、開発コストが膨大になると ともに、チップレベルでの積層であるためにスループットが低くなってしまう。この問題を解決するために、 産業技術総合研究所の九州センターが中心にとなって、ミニマルファブ方式による 3 次元集積回路の生 産システム (ミニマル 3D-IC ファブ(図 1-1-1(c)))を推進している. ミニマル 3D-IC ファブ方式での積層で は、0.5 インチウエハ、大口径ウエハから切り出したチップを、ミニマルファブ装置で加工し、良品チップの みを積層する。それゆえ、初期投資を抑えることができ、高い歩留まりを実現することができる。

図 1-1-1: 3 次元集積回路の作製手法の比較。(a) WOW (Wafer on Wafer)。(b) COC (Chip on Chip) )。(c) ミニマル 3D-IC ファブ方式)。

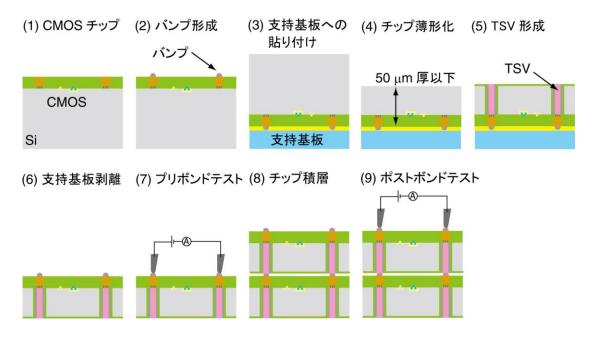

図 1-1-2 に、ミニマル 3D-IC ファブ方式での 3 次元集積回路作製プロセスの例を示す。この工程では、(1)ハーフインチサイズのウエハ、(2) 従来プロセスで形成した大口径ウエハから切り出した 10 mm 角チップ、の両方を対象として、via last 工程による 3D-IC 作製を実施する。ウエハ (チップ)表面にマイクロバンプを形成した後に、支持基板の貼り付けを行い、ウエハ (チップ)の薄形化を行う。次に、シリコン貫通電極を形成する。さらに、支持基板を剥離した後、プリボンドテストを行い、バンプやシリコン貫通電極に不良があるチップを排除する。その後、良品チップのみを積層する。チップ積層後、ポストボンドテストを行い、良品の積層チップのみを選び、パッケージングを行い、最終検査を行う。

本研究開発では、(7) プリボンドテストと(9) ポストボンドテストに対応するような検査装置を開発する。

図 1-1-2: ミニマル 3D-IC ファブ方式での 3 次元集積回路作製プロセスの例。

#### (2) 研究目的

本研究開発では、ミニマル 3 次元集積回路製造(ミニマル 3D-IC ファブ)ライン用の検査評価システムを開発する。

エスティケイテクノロジー社が、パーソナル超小型デバイス検査装置に用いている検査専用 LSI 技術に、VXI・PXI モジュール技術などを組み合わせることで、ミニマルファブ装置規格(幅 30 cm・奥行き 4 5 cm・高さ 144 cm)に収納でき、しかも 3 次元集積回路の電気特性評価と検査を行える計測部を開発する。また、産業技術総合研究所が、 $20\sim50~\mu m$  という微細ピッチに対応し、数百ピンレベルのコンタクト性能を有するコンタクトバンプ技術を発展させて、(1) ミニマルファブ仕様(10~mm 角)・LSI チップの薄膜電極( $50\sim100~\mu m$  ピッチ程度)に対応したプロービング技術、(2) ミニマル 3 次元集積回路のシリコン貫通電極(TSV: Through-Si-Via)へのプロービング技術( $20\sim50~\mu m$  ピッチ程度)を開発する。この両者の技術を組み合わせることにより、ミニマル 3 次元集積回路製造(ミニマル 3D-IC ファブ)ライン用の検査評価システムを構築する。

# (3) 目標(実施内容)

本研究の具体的な実施内容は以下のとおりである。

【1】ミニマル3次元積層 LSI デバイス製造ファブに対応したデバイス検査装置計測部の開発

①【1-1】ミニマル 3 次元積層 LSI デバイス製造ファブに対応したデバイス検査装置計測部の設計 平成 23 年度に、エスティケイテクノロジーが、パーソナル超小型デバイス検査装置に用いている検査専用 LSI 技術に、PXI バスモジュール技術を組み合わせることで、ミニマル 3 次元積層 L

SI デバイス製造ラインに対応したデバイス検査装置計測部の設計を行った。具体的には、ミニマルファブ装置規格(幅 30 cm・奥行き 45 cm・高さ 144 cm)に収納できるように、計測部の仕様を最適化した。計測部の主な仕様は、デバイス電源が 5 系統、チャネル数が 128 であり、各チャネルの電圧や電流を測定できるとともに、2 種類のタイミング計測機能を有している。

#### ②【1-2】デバイス検査装置計測部の試作

平成 23 年度に、【1-1】の設計に基づき、エスティケイテクノロジーが、ミニマル 3 次元積層 LSI デバイス製造ラインに対応したデバイス検査装置の計測部を試作した。ミニマルファブ装置規格(幅 3 0 cm・奥行き 45 cm・高さ 144 cm)に納まるような、小型の計測部を実現した。また、【2-2】のプローブ部と電気的に接続するためのポゴリングやテスター基板を試作した。

# ③【1-3】試作したデバイス検査装置計測部の基本特性評価

平成24年度は、エスティケイテクノロジーが産業技術総合研究所と共同で、試作したデバイス 検査装置計測部の電気評価項目に関して、基本特性評価を実施した。評価対象として、薄膜電極つ きチップ(プローブ接触抵抗評価用チップとフラッシュメモリチップ)とシリコン貫通電極つき3次元積層 チップを想定した評価手法及び評価項目の検討を行った。

# 【2】ミニマル 3 次元積層 LSI デバイス製造ファブに対応したデバイス検査装置プローブ部の開発

#### ④【2-1】デバイス検査装置プローブ部の設計

平成 23 年度に、産業技術総合研究所が、ミニマル 3 次元積層 LSI デバイス製造ファブに対応したデバイス検査装置プローブ部の設計を行った。 具体的には、(1) 積層前の、ミニマルファブ仕様 (10 mm 角)・LSI チップの薄膜電極(100  $\mu$ m ピッチ程度)に対応したプロービング技術、(2) ミニマル 3 次元積層 LSI デバイスのシリコン貫通電極へのプロービング技術(50  $\mu$ m ピッチ程度)を行えるように、デバイス検査装置プローブ部の設計を行った。

#### (5)【2-2】デバイス検査装置プローブ部の試作

平成 23 年度に、産業技術総合研究所が、ミニマルファブ仕様に精通したモジュール・部品メーカーなどの協力支援を得ながら、ミニマル 3 次元積層 LSI デバイス製造ファブ対応のデバイス検査装置プローブ部を試作した。具体的には、ミニマルファブ仕様(10 mm 角)チップ上の 100  $\mu$ m ピッチの薄膜電極に対応した、デバイス搭載機構(プロービング容器や検査ステージなど)とデバイスコンタクト機構(コンタクトシート)を試作した。平成 24 年度は、20~50  $\mu$ m ピッチの薄膜電極やシリコン貫通電極に対応可能なデバイス搭載機構とデバイスコンタクト機構を試作した。

#### ⑥【2-3】試作したデバイス検査装置プローブ部の基本特性評価

平成24年度に、産業技術総合研究所がエスティケイテクノロジーと共同で、試作したデバイス 検査装置プローブ部の電気評価項目に関する基本特性評価を実施した。また、試作したデバイス検査 装置プローブ部を用いて検査する際の課題を検討した。検査対象としては、薄膜電極つきチップ(プローブ接触抵抗評価用チップとフラッシュメモリチップ)、シリコン貫通電極つき3次元積層チップとした。

#### 【3】ミニマル 3 次元積層 LSI デバイス製造ファブに対応したデバイス検査装置の統合化

⑦【3-1】ミニマル 3 次元積層 LSI デバイス製造ファブに対応したデバイス検査装置の統合化モデルの設計

平成 24 年度に、エスティケイテクノロジーが産業技術総合研究所と共同で、ミニマル 3 次元積層 LSI デバイス製造ラインに対応したデバイス検査装置の統合化モデルの設計を実施した。

#### ⑧【3-2】デバイス検査装置の統合化モデルの試作(自動検査制御モジュール)

平成 24 年度に、エスティケイテクノロジーが産業技術総合研究所と共同で、ミニマル 3 次元積層 LSI デバイス製造ラインに対応したデバイス検査装置の統合化モデルの試作を実施した。平成 25 年度は、ミニマル規格の適合を図るための筺体内部のレイアウトの見直しと、自動検査動作を実行す

るための操作プログラムの拡充を図る。具体的な開発実施内容は以下のとおりである。

- (a) デバイス検査装置計測部およびプローブ部を、すべてミニマル筐体に収める。

- (b) デバイス検査装置プローブ部やテスター基板を交換しやすくするための部品改造を行う。

- (c) ミニマル筐体内部のパーティクル/ごみを低減するための部品導入を行う。

- (d) チップ搬送時間を短くするための部品改造を行う。

- (e) 自動検査動作への対応が可能で、エラー処理を有し、ミニマル規格に適合する操作プログラムを開発する。

# ⑨【3-3】デバイス検査装置の統合化モデルの総合評価

平成 24 年度に、エスティケイテクノロジーと産業技術総合研究所で、ミニマル 3 次元積層 LSI デバイス製造ラインに対応したデバイス検査装置の統合化モデルの試作を実施した。又、これを用いアラインメント精度及びスループットの性能評価を行った。

# (a)アライメント精度

- •50-100  $\mu m$  ピッチ LSI チップ上の薄膜電極へのプロービングに必要とされるアライメント精度  $\pm$  10  $\mu m$  は、24 年度開発で達成した。これにより 50-100  $\mu m$  ピッチ LSI チップのプロービングテストは可能となった。

- •20-50  $\mu m$  ピッチのシリコン貫通電極 (TSV) へのプロービングに必要とされるアライメント精度は $\pm 3~\mu m$  程度である。現時点では $\pm 10~\mu m$  程度であったが、アライメント処理を繰り返すこと等で精度向上が出来る見通しを得た。

- (b)電気特性の精度測定

- 24 年度は実施せず。25 年度検証予定

- (c)スループット

ミニマル装置の1プロセスの処理時間の目標値は概ね1分とされている。シャトルからチップの取り出し→チップ搬送→チップアライメント→コンタクト→チップ搬送→シャトルへのチップ格納までの時間 (ただし、デバイスをテストする時間を除く)は現状 90 秒程かかっている。機械構造の改造、ソフトウェアの改良等により時間短縮を行うことで目標値に近づける計画である。

平成 25 年度は、試作(⑧含む)したデバイス検査装置の統合化モデルについて、アライメント精度、電気特性の測定精度、スループット等を含め、総合的な性能評価を行う。また、フラッシュメモリチップとシリコン貫通電極つき 3 次元積層チップ及び MEMS チップの検査に固有の課題を検討する。統合化モデルの総合評価における目標値は以下のとおりである。

#### (a)アライメント精度

20-50 μm ピッチのシリコン貫通電極(TSV)へのプロービングを実現するために、アライメントマークの画像処理検出手法の改善やアライメントマークのコントラスト認識の改善等を行い、アライメント精度±3 μm を達成する。

# (b)電気特性の測定精度

一般的なメモリ系 IC においてリーク電流は $\pm 10~\mu A(max)$ 程度の仕様である。メモリ系 IC のリーク電流を測定するためには、測定対象の 1/10 程度の測定精度がミニマル対応 IC SI 検査装置として要求されている。同様に電圧測定精度も、電源電圧  $10~\mu A(max)$  程度の 1/10 程度の測定精度の 1/10 程度の測定精度の 1/10 程度の測定特度の 1/10 RV の電圧測定精度が要求されている。このため以下を目標とする。

・電流測定精度 : ±1 μA (レンジ 32 μA)

•電圧測定精度 : ±10 mV

#### (c)スループット

シャトルからチップ取り出し→シャトルヘチップ格納までの 1 プロセス時間: 1 分以内 (デバイステスト時間を除く)とする。

# 1-2 研究体制

# (1) 研究組織(全体)

# 総括研究代表者(PL)

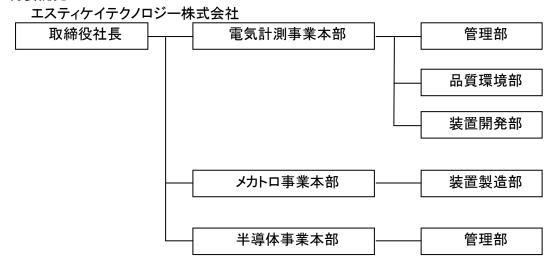

所属:エスティケイテクノロジー株式会社

役職:電気計測事業本部装置開発部 課長

氏名:川野 健二

# 副総括研究代表者(SL)

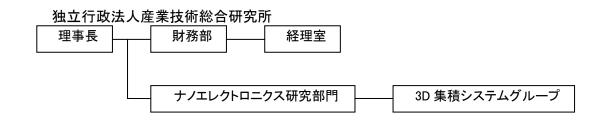

所属:独立行政法人産業技術総合研究所

役職:ナノエレクトロニクス研究部門 副研究部門長

氏名:青柳 昌宏

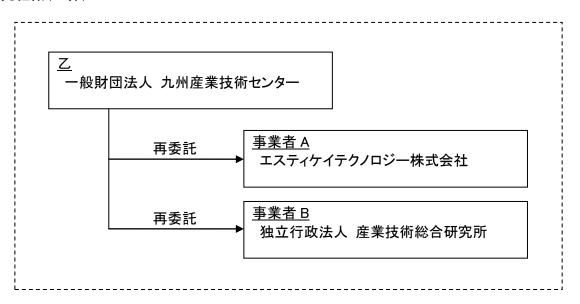

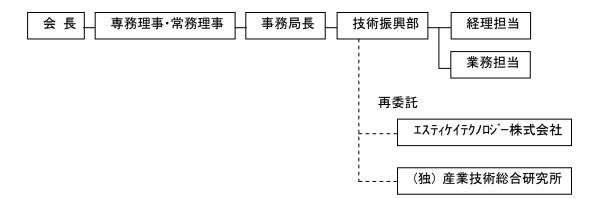

# (2) 管理体制

#### ① 事業管理者

一般財団法人九州産業技術センター

# ② 再委託先

# (3) 管理員及び研究員

# 【事業管理者】一般財団法人 九州産業技術センター

# ①管理員

| 氏 名    | 所属•役職    | 実施内容(番号) |

|--------|----------|----------|

| 二階堂 正憲 | 技術振興部長   | 10       |

| 野田彰    | 技術振興部 部長 | 10       |

| 高尾 喜則  | 技術振興部 次長 | 10       |

| 濱田 和彦  | 技術振興部 次長 | 10       |

# ②研究員

| 氏 名 | 所属•役職 | 実施内容(番号) |

|-----|-------|----------|

| 無し  |       |          |

# 【再委託先】※研究員のみ

# エスティケイテクノロジー株式会社

| 氏 名    | 所属·役職                | 実施内容(番号) |

|--------|----------------------|----------|

| 川野健二   | 電気計測事業本部 装置開発部 課長    | 8,9      |

| 江藤 道之  | 電気計測事業本部 品質環境部 次長    | 8,9      |

| 高橋 剛   | 電気計測事業本部 装置開発部 係長    | 8,9      |

| 笹島 輝幸  | 電気計測事業本部 装置開発部 主任技術員 | 8,9      |

| 姫野 健一郎 | 電気計測事業本部 装置開発部       | 8,9      |

| 久本 裕司  | 電気計測事業本部 装置開発部 副技師   | 8,9      |

| 亀川 晃   | 電気計測事業本部 装置開発部 副技師   | 8,9      |

| 池田 孝行  | 電気計測事業本部 装置開発部       | 8,9      |

| 小林 光彦  | メカトロ事業本部 装置製造部 主任技術員 | 8,9      |

# 独立行政法人産業技術総合研究所

| 氏 名   | 所属•役職                        | 実施内容(番号) |  |  |  |

|-------|------------------------------|----------|--|--|--|

| 青柳 昌宏 | ナノエレクトロニクス研究部門 副研究部門長        | 9        |  |  |  |

| 菊地 克弥 | ナノエレクトロニクス研究部門 主任研究員         | 9        |  |  |  |

| 渡辺 直也 | ナノエレクトロニクス研究部門 主任研究員         | 9        |  |  |  |

| 原 史郎  | ナノエレクトロニクス研究部門 ミニマルシステムグループ長 | 9        |  |  |  |

|       |                              |          |  |  |  |

# (4) 他からの指導・協力者名及び指導・協力事項

研究推進委員会委員

(外部推進委員)

| 氏 名    | 所属•役職                                  | 備考     |

|--------|----------------------------------------|--------|

| 井上 道弘  | (独)産業技術総合研究所 研究参与                      | アドバイザー |

| 原清明    | 株式会社堀場エステック専務取締役                       | アドバイザー |

| 小切間 正彦 | 株式会社メムス・コア 専務取締役                       | アドバイザー |

| 高橋 健司  | 株式会社東芝セミコンダクター&ストレージ社<br>メモリパッケージ開発部参事 | アドバイザー |

# (内部推進委員)

| 氏 名    | 所属·役職                                           | 備考   |

|--------|-------------------------------------------------|------|

| 二階堂 正憲 | 一般財団法人 九州産業技術センター<br>技術振興部長                     | 事務局  |

| 野田彰    | 一般財団法人 九州産業技術センター<br>技術振興部 部長                   | 事務局  |

| 高尾 喜則  | 一般財団法人 九州産業技術センター 技術振興部 次長                      | 事務局委 |

| 濱田 和彦  | 一般財団法人 九州産業技術センター 技術振興部 次長                      | 事務局委 |

| 山崎 恵   | エスティケイテクノロジー株式会社<br>常務取締役                       |      |

| 江藤 道之  | エスティケイテクノロジー株式会社 電気計測事業本部 品質環境部 次長              | 委    |

| 川野 健二  | エスティケイテクノロジー株式会社<br>電気計測事業本部 装置開発部 課長           | PL委  |

| 衛藤 和久  | エスティケイテクノロジー株式会社<br>半導体事業本部 管理部 次長              |      |

| 青柳 昌宏  | 独立行政法人 産業技術総合研究所 ナノエレクトロニクス研究部門 副研究部門長          | SL   |

| 渡辺 直也  | 独立行政法人 産業技術総合研究所 ナノエレクトロニクス研究部門 主任研究員           |      |

| 原 史郎   | 独立行政法人 産業技術総合研究所 ナノエレクトロニクス研究部門 ミニマルシステムグ・ループ 長 |      |

# 研究小委員会委員

# (内部推進委員)

| п д    | ᇎᇛᄱᄥ                                            | /# <del>**</del> |

|--------|-------------------------------------------------|------------------|

| 氏 名    | 所属・役職                                           | 備考               |

|        |                                                 |                  |

| 二階堂 正憲 | <br>  一般財団法人 九州産業技術センター<br>  技術振興部長             | 事務局              |

| 野田彰    | 一般財団法人 九州産業技術センター<br>  技術振興部 部長                 | 事務局              |

| 高尾 喜則  | 一般財団法人 九州産業技術センター<br>技術振興部 次長                   | 事務局委             |

| 濱田 和彦  | 一般財団法人 九州産業技術センター<br>技術振興部 次長                   | 事務局委             |

| 山崎 恵   | エスティケイテクノロジー株式会社<br>常務取締役                       |                  |

| 江藤 道之  | エスティケイテクノロジー株式会社 電気計測事業本部 品質環境部 次長              | 委                |

| 川野 健二  | エスティケイテクノロジー株式会社<br>電気計測事業本部 装置開発部 課長           | PL委              |

| 衛藤 和久  | エスティケイテクノロジー株式会社<br>半導体事業本部 管理部 次長              |                  |

| 青柳 昌宏  | 独立行政法人 産業技術総合研究所<br>ナノエレクトロニクス研究部門 副研究部門長       | SL               |

| 渡辺 直也  | 独立行政法人 産業技術総合研究所 ナノエレクトロニクス研究部門 主任研究員           |                  |

| 原史郎    | 独立行政法人 産業技術総合研究所 ナノエレクトロニクス研究部門 ミニマルシステムグ・ループ 長 |                  |

<sup>(</sup>注)・研究員(労務費を委託対象にする)には、<br/>

を備考欄に記載。

# 1-3 成果概要

デバイス検査装置の統合化モデルの試作結果と総合評価結果を表 1-3-1 と表 1-3-2 に示す。 概ね目標を達成することができた。

表 1-3-1: デバイス検査装置の統合化モデルの試作結果

| 計画                                               | 結果                                                                                                                        | 評価 |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----|

| デバイス検査装置計測部およびプローブ部<br>を、すべてミニマル筺体に収める。          | 内部レイアウトの見直し及び、小型部品の<br>採用を図り、すべてを筐体内に収める事<br>が出来た。                                                                        | 0  |

| デバイス検査装置プローブ部やテスター基<br>板を交換しやすくするための部品改造を行<br>う。 | プローブ部のコンタクトシート及びテスター<br>基板の交換おいて、その固定方法を見直<br>し、簡易に交換出来るように改良した。                                                          | 0  |

| ミニマル筐体内部のパーティクル/ごみを低減するための部品導入を行う。               | HEPA フィルターやファンを取り付け、検査空間の清浄化を行い、パーティクル低減を実施した。                                                                            | 0  |

| チップ搬送時間を短くするための部品改造を行う。                          | 前室である PLAD2 (Particle Lock Air -tight Docking)の取り付け位置を変えて、ステージの可動距離を短縮した。                                                 | Δ  |

| 自動検査動作への対応が可能で、エラー処理を有し、ミニマル規格に適合する操作プログラムを開発する  | エラー処理を含めた自動検査動作を行う<br>ソフトウェアを開発し、ミニマルファブ規格<br>のタッチパネルへの変更及びユーザーイ<br>ンタフェース等のソフトウェアの修正を行<br>い、ミニマル規格に適合する操作プログラ<br>ムを開発した。 | 0  |

表 1-3-2: デバイス検査装置の統合化モデル評価結果

| 項目       | 目標値                  | 結果                                    | 評価 |

|----------|----------------------|---------------------------------------|----|

| アライメント精度 | ±3 μm 以下             | ±2 μm 以下                              | 0  |

| 電流測定精度   | ±1 μA<br>(レンジ 32 μA) | +0.031 μA<br>-0.005 μA<br>(レンジ 32 μA) | 0  |

| 電圧測定精度   | ±10 mV               | +0.358 mV<br>-2.092 mV                | 0  |

| スループット   | 60 s                 | 108 s                                 | Δ  |

# 1-4 当該研究開発の連絡窓口

# 【事業管理者】

・一般財団法人 九州産業技術センター

技術振興部 部長 野田 彰

TEL:092-411-7394 FAX:092-472-6688 E-Mail:noda@kitec.or.jp

# 【研究者】

・エスティケイテクノロジー株式会社

電気計測事業本部 装置開発部 課長 川野 健二

TEL: 097-527-2190 FAX: 097-521-1438

E-Mail: kawa@stk-net.co.jp

•独立行政法人 産業技術総合研究所

ナノエレクトロニクス研究部門 副研究部門長 青柳 昌宏

TEL: 029-861-5529 FAX: 029-862-6511

E-Mail:m-aoyagi@aist.go.jp

# 第2章 本論

#### 2-1 デバイス検査装置計測部の開発

本節では、ミニマル 3 次元積層 LSI デバイス製造ファブに対応したデバイス検査装置計測部の 開発を行った結果を示す。

#### 2-1-1 デバイス検査装置計測部の設計

# (1) 計測部基本仕様

ミニマルファブ構想及び、3次元積層 LSI デバイスへ対応するための、計測部の仕様を策定し た。具体的には、ミニマル装置筺体に収納出来るシステムである事と、機能及び性能に対し拡張 性を持たせる事等が主要な前提条件となる。これらを踏まえ、仕様を決定した。 以下に計測部の仕様を示す。

#### (2) システム構成

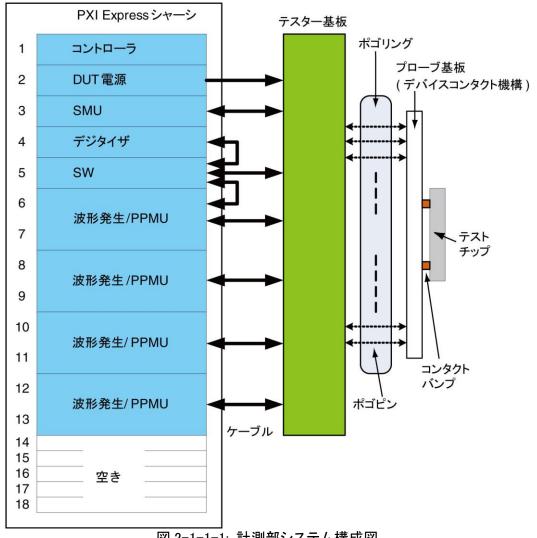

図 2-1-1-1に、計測部のシステム構成を示す。

本システムは、PXI バスシステムを構築する測定機器本体部と、コンタクトシートと接続するテス ター基板で構成される。測定機器本体とテスター基板は、専用ケーブルで接続され、テスター基板 とコンタクトシートは、ポゴピンにて電気的に接続される構造を有する。

図 2-1-1-1: 計測部システム構成図

# (3) 測定機器仕様

測定機器本体は、PXI バスシステムをベースに計測機能を有する基板を組み合わせ、デバイス 検査に必要な機能の最適化を図った。

計測部における、主要測定機能を測定機器本体シャーシのスロット毎に、表 2-1-1-1 に示す。 尚、ミニマル筐体に収容するには、9 スロットの測定器シャーシを採用し、テスト対象及びテスト内 容に沿って、機能別のボードを選択し測定機能を構成する事とした。

表 2-1-1-1: 各スロットにおける測定用ボード仕様

| No, | ボード名称     | 内容                                                          | 仕様概要                                                        |

|-----|-----------|-------------------------------------------------------------|-------------------------------------------------------------|

| 1   | コントローラ    | 1.73GHz クアッドコア Int<br>el Core i7-820 プロセッ<br>サ、DDR3 RAM 2GB | GPIB、シリアル、1000BaseTX Ethern<br>et、ExpressCard/34 スロット、4xUSB |

| 2   | DUT 電源    | トリプル出力プログラマブ<br>ル DC 電源                                     | 最大 9W、16 ビット電圧設定ポイント<br>および電流制限、16 ビット電圧/電流<br>フィードバック      |

| 3   | SMU       | ソースメジャーユニット                                                 | 4 象限動作、最大 10W シンク、±20<br>V、2A、絶縁出力、リモートセンス                  |

| 4   | デジタイザ     | 250MS/s、8 ビットデジタ<br>イザ                                      | 125MHz 帯域幅、2ch 同時サンプリング、40mV~40V 入力信号範囲                     |

| 5   | スイッチ      | 高速デジタル IO 信号挿<br>入スイッチ                                      | 最大クロックレート 200MHz、35 デジタ<br>ル IO パススルーライン                    |

| 6   | 波形発生/PPMU | 200MHz デジタル波形ア<br>ナライザ、PPMU 付                               | ダイナミックデータ 24ch、制御 4c<br>h (各チャンネルに PPMU 付)、-2~+7<br>V、±32mA |

| 7   |           |                                                             | 1, ===:::                                                   |

| 8   | 同上        | 同上                                                          | 同上                                                          |

| 9   | 1712      | 17.1                                                        | 17.1                                                        |

| 10  | 同上        | 同上                                                          | 同上                                                          |

| 11  |           |                                                             |                                                             |

| 12  | 同上        | 同上                                                          | 同上                                                          |

| 13  | , .       | , .                                                         |                                                             |

| 14  | 未実装       | -                                                           |                                                             |

| 15  | 未実装       | -                                                           |                                                             |

| 16  | 未実装       | -                                                           |                                                             |

| 17  | 未実装       | -                                                           |                                                             |

| 18  | 未実装       | _                                                           |                                                             |

# (4) テスター基板仕様

テスター基板は、各測定機器からのテスト信号をケーブル接続し、ポゴピンを介してコンタクトシートへ中継するための基板回路である。本基板仕様を表 2-1-1-2 に示す。

表 2-1-1-2: テスター基板仕様

| 項目      | 仕様                                                                                                                                          |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 形状      | 100mm×200mm×、板厚:2.0mm                                                                                                                       |

| 層数      | 10 層                                                                                                                                        |

| シルク     | 両面(白色)                                                                                                                                      |

| レジスト    | 両面(緑色)                                                                                                                                      |

| 表面処理    | 無電解金メッキ                                                                                                                                     |

| インピーダンス | $50\Omega \pm 5\Omega$                                                                                                                      |

| 部品実装    | 片面  •12 ピンコネクタ  型式:MSTBVA 2.5/12-G-5.08 (Phenix Contact K.K.)  数量:1 個  •68 ピンコネクタ  型式:R-HS-008068-1B (All Best Electronics Co.,Ltd)  数量:8 個 |

# 2-1-2 デバイス検査装置計測部の試作

# (1) 計測部の試作結果

前述の仕様に基づき、試作を行った。

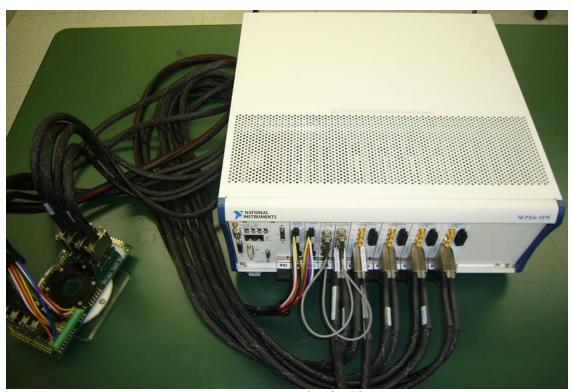

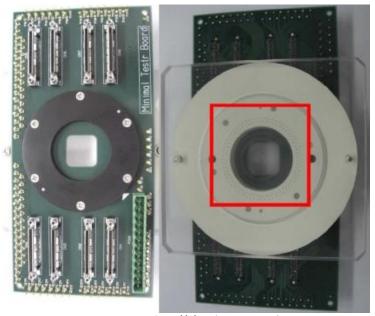

図 2-1-2-1 に計測部全体の外観を示す。図 2-1-2-2 にテスター基板及びポゴリングの外観を示す。

図 2-1-2-1: 計測部外観

図 2-1-2-2: テスター基板(左:上面、右:下面)

# (2) 計測部システムソフトウェア

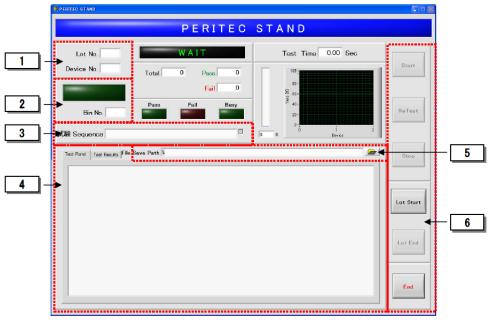

デバイス検査に関する、電流・電圧の直流特性と、時間軸特性及び周波数特性を測定評価するためのソフトウェアを開発した。

以下にそのソフトウェアのユーザーインタフェースを示す。また、測定用のテストプログラムは、個々に異なる被試験デバイス(DUT)に合うように個別のプログラミングが必要であり、これを含めたシステムソフトとなっている。

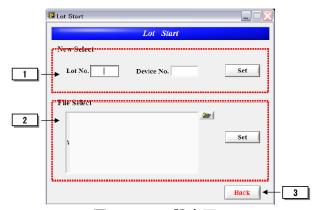

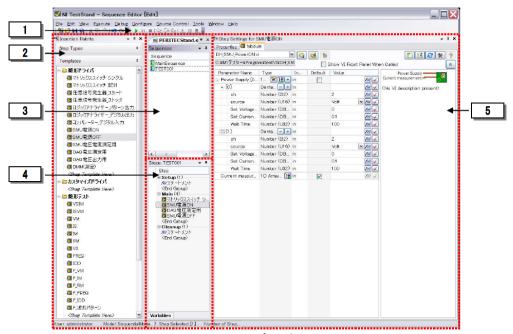

デバイス検査を実行する際に用いる、操作画面を図 2-1-2-3 に示す。ロット/デバイス No を設定する際に用いる. 設定画面を図 2-1-2-4 に示す。テストプログラムを作成編集する際に用いる. 編集画面を図 2-1-2-5 に示す。

図 2-1-2-3: 操作画面

図 2-1-2-4: 設定画面

図 2-1-2-5: テストプログラム編集画面

# 2-1-3 デバイス検査装置計測部の基本特性評価

デバイス検査装置計測部の電気評価項目に関して、基本特性評価を実施した結果を示す。評価対象として、プローブ接触抵抗評価、フラッシュメメモリチップによる評価及び、シリコン貫通電極つき3次元積層チップを想定した。それらの評価手法と評価結果を示す。

# (a) プローブ接触抵抗の評価

#### (1) 評価方法

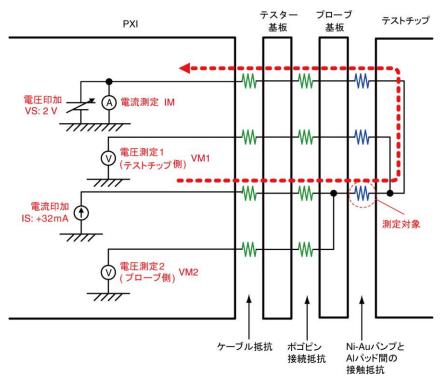

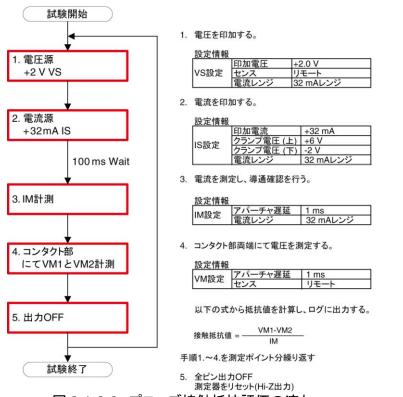

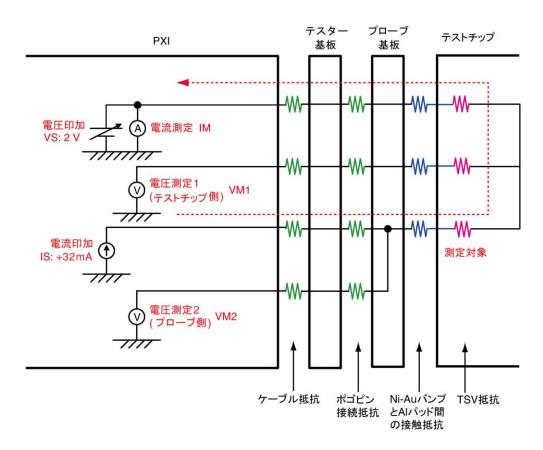

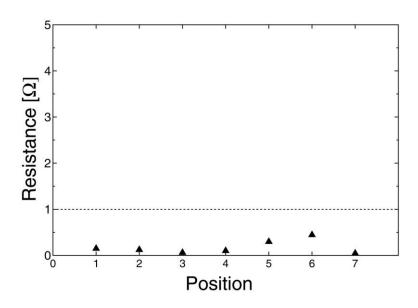

図 2-1-3-1 にプローブ接触抵抗測定の簡易回路図を示し、図 2-1-3-2 にプローブ接触抵抗測定の流れを示す。まず、電圧(VS)印加と電流(IS)印加を行う。100~ms 経過後に、電流(IM)計測を行い、テストチップ側の電位 VM1 とプローブ側の電子 VM2 を計測する。(VM1-VM2)/IM を計算することにより、Ni-Au バンプと Al パッド間の接触抵抗が得られる。接触抵抗の評価判定基準としては、実用レベルと考えられる  $1~\Omega$ 以下とした。

ここで、得られる接触抵抗の測定誤差について検討する。VM1、VM2、IM の測定精度は、表 3-1-1-1-1 より、±3 mV、±3 mV、±0.32 mA (32 mA モードの場合)である。それゆえ、接触

# 抵抗は、

接触抵抗=|(VM1 の値±3 mV- VM2 の値±3mV) / (32mA±0.32mA)| =|(VM1 の値-VM2 の値) / (32mA±0.32mA)| ±|6mV / (32mA±0.32mA)|

となるので、大きい場合に、おおよそ 6 mV/(32 mA-0.32 mA)= $\pm 0.19$   $\Omega$ 程度の誤差が含まれることとなる。

図 2-1-3-1: プローブ接触抵抗測定の簡易回路図。

図 2-1-3-2: プローブ接触抵抗評価の流れ。

# (2) 評価結果

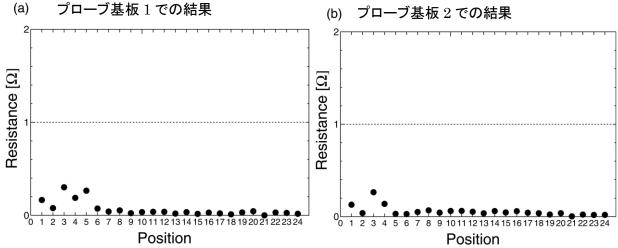

図 2-1-3-3 に、2 つのプローブ基板を用いて 24 箇所におけるプローブ接触抵抗の評価した結果を示す。すべての箇所で、1Ω以下の安定した接触抵抗値が得られている。このことから、プロービングができていることを確認した。ただし、前述した測定誤差を含んでいるので、より精密な計測を行うためには、VM1 と VM2 の測定誤差を小さくする必要がある。

図 2-1-3-3: プローブ接触抵抗の測定結果(プローブピッチ:100µm の場合)。

#### (b)フラッシュメモリによる評価

#### (1) プローブ基板とフラッシュメモリチップ

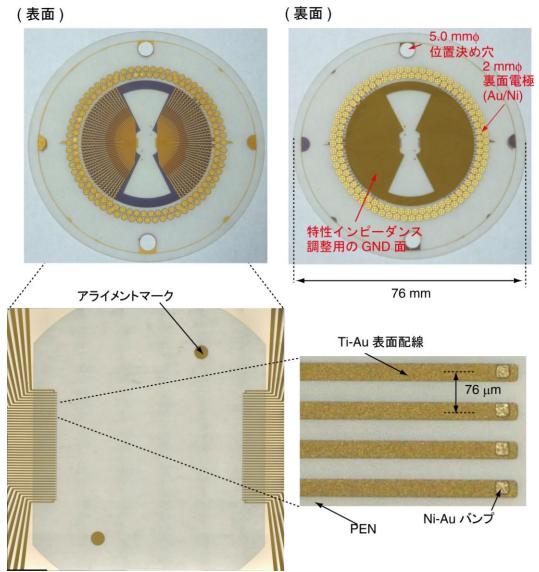

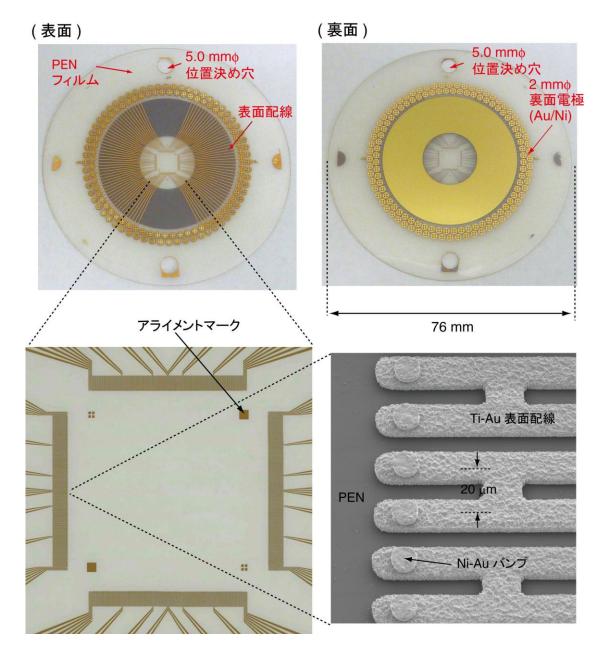

フラッシュメモリチップの評価用のプローブ基板として、PEN(ポリエチレンナフタレート)を基本材料とするプローブ基板を製作した。ポリイミド型プローブ基板よりも若干硬いが、非常に透過性が高いため、プロービング時のアライメント動作において、カメラでのアライメントマークの視認性向上を図った。

図 2-1-3-4 に、評価に使用したフラッシュメモリチップの写真を示す。このチップは、SRAM(1M ビット:64k ビット×16)とフラッシュメモリ(8M ビット:512k ビット×16)を 1 チップに集積させたチップで、ロジックリサーチ社から提供いただいたものである。レイアウト上でのチップサイズは約 5.8 mm 角であるが、ミニマルファブ規格のチップサイズ(10mm 角)となるようにダイシングしている。図 2-1-3-5 に、PEN 型プローブ基板の写真を示す。125 $\mu$ m 厚の PEN フィルムに対して、表面側に配線と Ni-Au バンプがあり、裏面側に(ポゴピンと接触する) 裏面電極があり、それらが 0.4 mm $\phi$ の貫通電極で接続されている。Ni-Au バンプのサイズは、20 $\mu$ m 角、ピッチは 76 $\mu$ m で、バンプ高さは 6 $\mu$ m 程度である。

図 2-1-3-4: フラッシュメモリチップの写真。

図 2-1-3-5: フラッシュメモリチップ検査用の PEN 型の写真。

# (2) 評価方法

まず、フラッシュメモリチップの評価を行うにあたり、評価項目を検討した。中でも重要と考えられる、コンタクトチェック(ショートチェック)、入力ピンリークチェック、書き込み/読み出し動作の3つを実施することとした。以下に、それぞれの具体的な評価内容を示す。

# (2-1)コンタクトチェック

プロービングに問題がないこと、各入出力ピンの保護ダイオードに不良がないこと、他の入出力ピン/電源/GND とショートしていないことを確認するために実施する。全入出力ピン及び電源/GND を 0V にした状態で、測定ピンに対し-100µ A の電流を印加する。この時の電圧を測定し、保護ダイオードのみに電流が流れていることを確認する。具体的には、保護ダイオードの抵抗分による電圧降下が測定できれば良いとする。

# (2-2) 入力ピンリークチェック

入力ピン間のリーク電流を確認するために実施する。デバイス電源/GND を印加し、測定ピンのみ 0.0V(3.3V)を印加し、その他の入出力ピンは 3.3V(0.0V)を印加する場合のリーク電流を測定する。なお、0.0V 印加時の電流を IIL、3.3V 印加時の電流を IIH とする。評価判定基準は、 $\pm 2\mu$  A 以下とした。

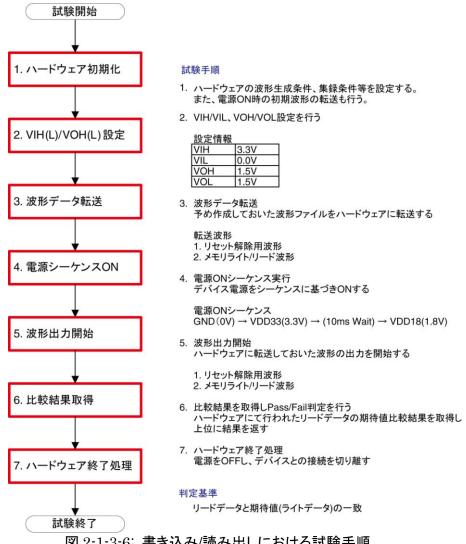

#### (2-3) 書き込み/読み出し動作

図 2-1-3-6 に、書き込み/読み出し動作における試験手順を示す。メモリ領域に対して書き 込み/読み出し動作を行い、メモリ領域に異常がないことを確認するために実施する。まず、 ハードウェア初期化・VIH、VILとVOH、VOLの設定を行った後に、ハードウェアに波形を転 送する。その後、デバイス電源をシーケンスに基づき ON にした後に、リセット解除信号の出力、 データ信号の出力(メモリへの書き込み)を行う。次に、メモリからのデータ信号の読み出しを行 い、期待値比較を行う。本来、ここではハードウェア上で読み出し値と期待値の比較を行いそ の結果だけを取得するため、詳細なデータは残らないが、今回は、視覚に波形確認を行うため、 波形データを保存する機能を追加している。最後に、電源を OFF にし、デバイスとの電気的接 続を解除する。

図 2-1-3-6: 書き込み/読み出しにおける試験手順。

#### (3) 評価結果

#### (3-1) コンタクトチェックの結果

プロービングを行っていない場合には、-1.98V~-2V が計測され、プロービングを行った場合 には、-0.52~-0.55V 程度の電圧が計測され、各端子の保護ダイオードの ON 状態を確認す ることができた。また、繰り返し測定ばらつきも、1mV(標準偏差)と十分に小さいことも確認した。

#### (3-2) 入力ピンリークチェックの結果

プロービングを行っていない場合には±4~5nA 程度の電流が計測されている。プロービン

グを行った場合には、プロービングを行っていない場合に比べて IIH が増加していることから、リーク電流を正常に測定できていると考えられる。 なお、カメラ照明が消灯時には、点灯時に 比較して IIH が 0~4nA 程度まで低下した。これは、保護ダイオードでの光電流の発生が抑制されるためである。

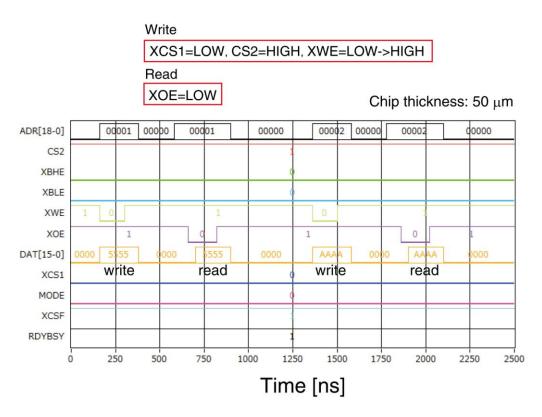

# (3-3) 書き込み/読み出し動作の結果

このフラッシュメモリチップ中の SRAM では、アドレス信号が入力されているときに、SRAM への書き込みは、信号 XCS=HIGH、CS=LOW 信号のときの XWE の立ち上がりで行われ、読み込みは信号 XOE=LOW のときに、読み込みが行われる。図 2-1-3-7 の実際の書き込み/読み出しの結果を見ると、直前に書き込んだデータがきちんと読み込まれていることを確認することができた。

図 2-1-3-7: 書き込み/読み出し動作の結果。

#### (c)シリコン貫通電極つき3次元積層チップの評価

#### (1) シリコン貫通電極つき3次元積層チップ

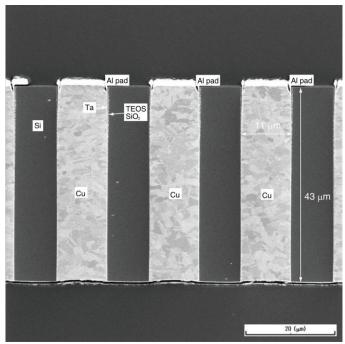

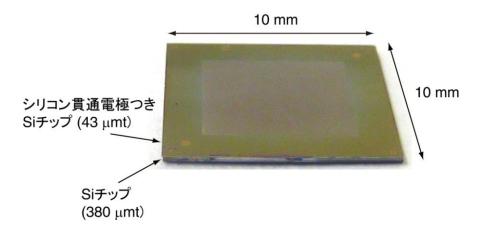

測定対象となるシリコン貫通電極つき 3 次元積層チップを製作した。作製工程は、8 インチの Si ウエハ( $725\mu m$ )に対して、ボッシュ方式によるドライエッチングにより、50  $\mu m$  程度の深穴を形成した。次に、TEOS-CVD SiO2 (500 nm 厚)を形成した後で、バリア膜・シード膜として、Ta-C u 膜を堆積した。その後、Cu 電解めっきで、Cu を充填する後で、Cu/Ta CMP を行い、不要な C u や Ta を除去する。次に、Ti-Al スパッタリングとフォトリソグラフィーと Al/Ti エッチングとレジスト除去を行い、表面電極の形成を行った。その後、バックグラインドとドライポリッシュを行い、Si ウエハを  $40\sim45\mu m$  厚程度まで薄形化したのちに、ダイシングを行った。次に、Si のエッチングを行った後で、全面に導電膜を形成した Si チップ ( $380\mu m$  厚)に積層した。

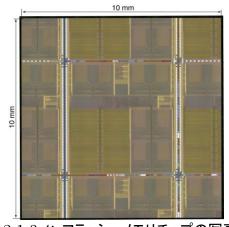

図 2-1-3-8 に、シリコン貫通電極つき薄形チップの断面 SEM 像を示す。表面側に Cu/Ta C MP 時のディッシングが若干発生しているものの、Cu がボイドなく充填されている。シリコン貫通電極の大きさは  $11\mu m$ 、ピッチは  $20\mu m$ 、長さは  $43\mu m$  である。

図 2-1-3-9 に、シリコン貫通電極つき 3 次元積層チップ (10mm 角サイズ)を示す。 薄形化した Si チップが割れることなく、下部の Si チップと積層できた。

図 2-1-3-8: シリコン貫通電極つき薄形 Si チップ

図 2-1-3-9: シリコン貫通電極つき 3 次元積層チップ (10mm 角サイズ)の写真。

# (2) 評価方法

まず、シリコン貫通電極つき3次元積層チップの評価を行うにあたり、コンタクトチェックを実施することとした。

図 2-1-3-10 に、コンタクトチェックにおける回路図を示す。プロービングに問題がないこと、シリコン貫通電極が表裏で導通していることを確認するために実施される。まず、電圧(VS)印加と電流(IS)印加を行う。100ms 経過後に、電流(IM)計測を行い、テストチップ側の電位 VM1 とプローブ側の電子 VM2 を計測する。(VM1-VM2)/IM を計算することにより、シリコン貫通電極の抵抗値 (プローブ接触抵抗を含む)が得られる。

図 2-1-3-10: シリコン貫通電極つき 3 次元積層チップに対するコンタクトチェック時の回路図。

# (3) 評価結果

$20\mu \text{m}$  ピッチプローブ基板を用いて、シリコン貫通電極つき 3 次元積層チップに対するコンタクトチェックを行った結果、シリコン貫通電極を含む形で導通が確認できたものの、得られた抵抗値は、最小でも  $10\Omega$ 程度と高かった。

図 2-1-3-11: シリコン貫通電極つき 3 次元積層チップに対する 4 端子測定結果。

# 2-2 デバイス検査装置プローブ部の開発

本節では、ミニマル 3 次元積層 LSI デバイス製造ファブに対応したデバイス検査装置プローブ部 (デバイス搭載機構とデバイスコンタクト機構)の設計を行った結果を示す。

#### 2-2-1 デバイス検査装置プローブ部の設計

# (1) デバイス搭載機構の設計

デバイス搭載機構の仕様について表 2-2-1-1 に示す。

デバイス検査装置のプロービング性能を、電極ピッチ  $100~\mu m$  から最少 20~mm までを目標に、プローブ部の開発を行った。

デバイス検査装置プローブ部は、テスト対象のチップを搬送し、アライメント動作を行うためのデバイス搬送機構と、テストチップとのコンタクト機能を有するデバイスコンタクト機構(プローブ基板)に分かれる。

デバイス搭載機構については、画像処理システムを用いたアライメント方式(アライメントマークの画像検出により、アライメントマークの位置座標を抽出し、その値をもとに、精密な XY・ステージを用いてデバイスチップを移動させて、アライメントを行う方法)を導入することで、位置精度を向上させることに成功した。

| 項目          | 条件                                                                                 |

|-------------|------------------------------------------------------------------------------------|

| 外部寸法        | ミニマル装置筐体(幅 30cm・奥行き 45cm・高さ 144cm)に<br>収まる寸法                                       |

| 電源          | AC100V                                                                             |

| 使用環境温度      | 10°C ~ 30°C                                                                        |

| 対応チップサイズと厚さ | サイズ: 9.97mm ~ 10.00mm<br>厚さ: 0.1mm 以上<br>※チップサイズは、ダイシング時のカット幅によって<br>変動しても対応可能とする。 |

| プロービング荷重    | 0 ~ 100 mNピン程度                                                                     |

| 必要なアライメント精度 | ±2μm 程度                                                                            |

表 2-2-1-1: デバイス搭載機構の仕様

#### 2-2-2 デバイス検査装置プローブ部の試作

図 2-2-2-1 に、試作した 20 μm ピッチ PEN 型プローブ基板の写真を示す。他に 50μm ピッチプローブも試作したが、20 μm ピッチプローブと共に非常に高歩留まりで作製することができた。 図 2-2-2-2 に、PEN 型プローブ基板のコンタクトバンプ(Ni-Au)付近の断面 SIM 像を示す。これより、Ti-Au 配線の表面粗さが大きいものの、その上に Ni がボイドなくめっきされていることが分かった。なお、Ti-Au 配線の表面粗さが大きいのは、(Ni バンプ前に行う)シードエッチング(Au/Ti エッチング)によるものであり、今後改善が必要である。

図 2-2-2-1: 20 μm ピッチ PEN 型プローブ基板の写真。

# 2-2-3 デバイス検査装置プローブ部の基本特性評価

# (1) 接触抵抗の評価方法

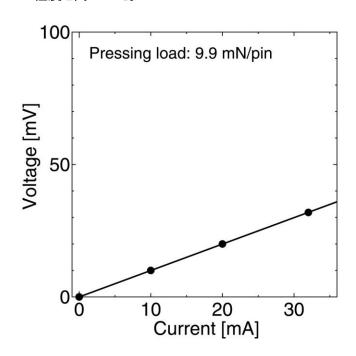

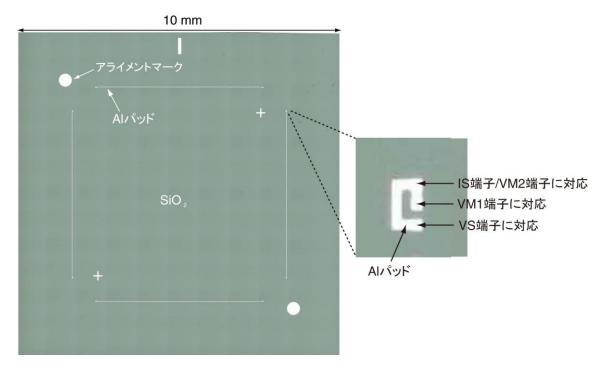

デバイスコンタクト機構(プローブ基板)の基本特性として、Ni-Au バンプと Al パッド間の接触抵抗を評価した。評価のために用意したプローブ基板は、20μm ピッチ PEN 型プローブ基板とした。また、それらに対応するテストチップの写真を図 2-2-3-1 に示す。10mm 角・380μm 厚の Si チップの上に熱酸化膜、Al パッドが形成されている。チップ上の 24 箇所に対して、4 端子測定法で、プローブ基板の Ni-Au バンプと Al パッド間の接触抵抗を計測できるようになっている。

評価手順は、まず、電圧(VS)印加と電流(IS)印加を行った後で、電流(IM)計測を行い、テストチップ側の電位 VM1 とプローブ側の電子 VM2 を計測した。その後、(VM1-VM2)/IM を計算することにより、Ni-Au バンプと Al パッド間の接触抵抗を取得した。接触抵抗の判定基準は、実用レベルと考えられる  $1\Omega$ 以下とした。

図 2-2-3-1: 20μm ピッチ Al 電極つきテストチップの写真。

# (2) 評価結果

図 2-2-3-2 に、 $20~\mu m$  ピッチプローブ基板を用いた場合の、24~ 箇所におけるプローブ接触抵抗の評価結果を示す。コンタクト荷重が増加するとともに、接触抵抗が低減している。すべての箇所で、 $1\Omega$ 以下の安定した接触抵抗値が得られている。このことから、プロービングができていることを確認した。

図 2-2-3-2: プローブ接触抵抗の測定結果

# 2-3 デバイス検査装置の統合化

本節では、デバイス検査装置の計測部とプローブ部の統合化および自動化のために行った結果を示す。

# 2-3-1 デバイス検査装置の統合化モデルの設計

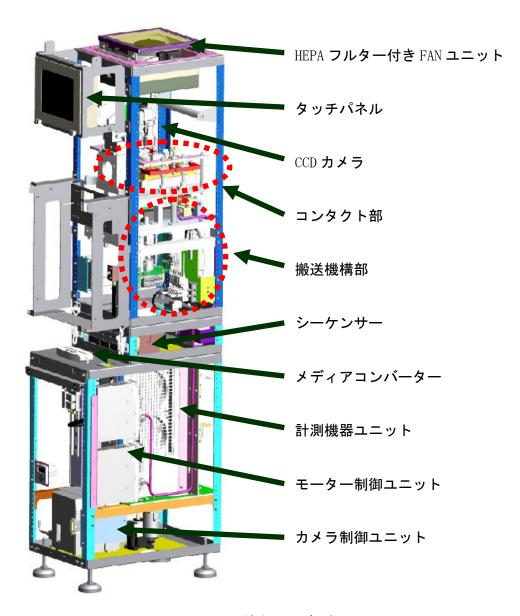

ミニマルファブ規格への適合を目的に、所要の機能を具備すると共に、ミニマルファブ規格の筐体に全ての機能及び機器を搭載するよう、レイアウト等を含め、再設計を行った。図 2-3-1-1 に本装置の概要を示す。

図 2-3-1-1: 統合化モデル概要図

# 2-3-2 デバイス検査装置の統合化モデルの試作

前項の設計に基づき、図 2-3-2-1 に試作した装置の外観写真を示す。

図 2-3-2-1:デバイス検査装置の外観写真。

# 2-3-3 デバイス検査装置の統合化モデルの総合評価

前項に示す試作機を使用し、アライメント精度、電気特性の測定精度、スループット評価を行った。統合化モデルの総合評価における結果は以下のとおりである。

# (a)アライメント精度

- ・ $50\sim100~\mu m$  ピッチ LSI チップ上の薄膜電極へのプロービングに必要とされるアライメント精度  $\pm10\mu~m$  は、24 年度開発で達成した。これにより  $50\sim100~\mu m$  ピッチ LSI チップのプロービングテストは可能となった。

- •50~20 $\mu$  m ピッチのシリコン貫通電極(TSV)へのプロービングに必要とされるアライメント精度は $\pm 3~\mu$ m 程度である。試作当初は、アライメント精度が $\pm 10~\mu$ m 程度であったが、アライメントマークの画像処理検出手法の改善やアライメントマークのコントラスト認識の改善等を行い、アライメント精度 $\pm 2~\mu$ m を達成した。

# (b)電気特性の精度測定

一般的なメモリ系 IC においてリーク電流は $\pm 10~\mu A(max)$ 程度の仕様である。メモリ系 IC のリーク電流を測定するためには、測定対象の 1/10 程度の測定精度がミニマル対応 LSI 検査装置として要求されている。同様に電圧測定精度も、電源電圧 3V 程度の NAN D フラッシュメモリにおいては、ミニマル対応 LSI 検査装置として $\pm 10mV$  の電圧測定精度が要求されている。このため以下を目標として設計した結果、下記の実力値を得る事が出来た。

・電流測定精度 : ± 1 μA (レンジ 32 μA)

→ 実力値 : +0.031 μA ~ -0.005 μA (レンジ 32 μA)

•電圧測定精度 : ±10 mV

→ 実力値 : +0.358mV ~ -2.092mV

# (c)スループット

ミニマルファブでは、プロセス処理時間を概ね 1 分程度を目安としている。本装置においてもシャトルからチップ取り出し、再度、シャトルへチップを格納するまでの時間を、1 分以内を目標とした。但し、デバイステスト時間は被測定物の仕様に依存するため、このテスト時間は除くものとした。

結果として、チップ搬送時間短縮のための搬送機構の可動距離短縮は改造範囲が多岐に渡るため、予算的に実施には至らなかった。但し、各ステージの可動距離短縮及びミニマル前室である PLAD2 の新式の採用等にて、目標とする 1 分程度の搬送時間は見込める事は確認した。

# 第3章 全体総括

# 3-1 本研究開発で得られた成果

本研究では、ミニマルファブ方式での3次元積層LSIデバイス製造ラインを構築するために必須となるデバイス検査装置を開発するために、以下の三つのテーマを掲げ開発を行った。

- ①ミニマル 3 次元積層 LSI デバイス製造ファブに対応したデバイス検査装置計測部の開発

- ②ミニマル 3 次元積層 LSI デバイス製造ファブに対応したデバイス検査装置プローブ部の開発

- ③ミニマル 3 次元積層 LSI デバイス製造ファブに対応したデバイス検査装置の統合化

- ①については、デバイス検査装置計測部の仕様検討を行い、PXI バスモジュール技術を組み合わせ、128 チャネルの測定が可能なデバイス検査装置の設計を行い、超小型のデバイス検査装置を試作した。また、②のプローブ部と電気的に接続するためのポゴリングやテスター基板を試作した。

②については、デバイス検査装置プローブ部(デバイス搭載機構とデバイスコンタクト機構)の設計を行い、(1) 積層前の、ミニマルファブ仕様(10 mm 角)・LSI チップの外部端子(100 μm ピッチ程度)に対応したプロービング技術を行える、(2) ミニマル 3 次元積層 LSI デバイスのシリコン貫通電極(T SV: Through-Silicon-Via)へのプロービング技術(20~50 μm ピッチ程度)を行える、という条件を満たすデバイス搭載機構とデバイスコンタクト機構を設計した。また、ミニマル装置規格に合うデバイス搭載機構を試作するとともに、デバイスコンタクト機構として Au バンプつきコンタクトシートと Ni-Au バンプつきコンタクトシートを試作した。

また、①で試作したデバイス検査装置計測部の電気評価項目に関して、基本特性評価を実施した。 プローブ抵抗評価用チップ、フラッシュメモリチップ、シリコン貫通電極つき 3 次元積層チップの 3 つを対象とした。 プローブ抵抗評価では、1 Ω以下の安定した接触抵抗が得ることができた。 フラッシュメモリチップの評価では、コンタクトチェック(ショートチェック)、入力ピンリークチェック、書き込み/読み出し動作の 3 つを行い、測定精度や再現性に問題なく実施できた。 また、シリコン貫通電極つき 3 次元積層チップの評価では、コンタクトチェックを行い、シリコン貫通電極を含む形で導通が確認できた。

また、デバイス検査装置プローブ部の開発として、 $50~20~\mu m$  ピッチ対応に向けて行ったデバイスコンタクト機構の(プローブ基板)の作製を行った。まず、 $50~20~\mu m$  という微細ピッチへの対応を行うために、ベース材料の変更やプローブ配線の形成方法の変更を実施した。さらに、バンプ部の耐久性を高めるために、バンプの材料として硬質金属(Ni など)を導入した。次に、そのプローブ部の基本特性として、テストチップ上の Al 電極との間で生じる接触抵抗を計測した。接触荷重が増加するとともに、接触抵抗の低減を確認でき、実用レベル( $1~\Omega$ 以下)となった。一方で、テストチップとプローブ基板間のパーティクルの噛みこみ、ステージとプローブ基板の平行度劣化などによるオープン不良も生じており、パーティクル対策の必要性が発生した。これは③のデバイス検査装置の統合化モデルの試作にて対策を施した。

③については、デバイス検査装置の統合化モデルの設計と試作を行った。ミニマル規格への適合を図るための筐体内部のレイアウトの見直しと、自動検査動作を実行するための操作プログラムの拡充を図った。総合評価結果として、(a)アライメント精度は $\pm 3\mu m$ 、(b) 電気特性の測定精度は、電流測定精度 :  $\pm 1~\mu A$  (レンジ  $32~\mu A$ )、電圧測定精度 :  $\pm 10~m V$  の目標精度を達成した。但し(c)スループットの目標  $60~\psi$ に対し  $108~\psi$ と目標を達成することはできなかった。この対策として、チップ搬送機構の可動距離の短縮及びミニマル前室である PLAD2 (Particle Lock Air-tight Docking)の新式の採用等にて目標を達成する見込みは得た。

全体としては、おおむね設計目標精度を達成し、デバイス検査装置の試作が出来たと考える。今後は、実用化への課題として、メンテナンス性の更なる向上や、スループットの課題解決に取り組んでいきたいと考える。

# 3-2 事業化への取り組み

今回開発したデバイス検査装置の販売先として、まずは、産業技術総合研究所や大学等の公的研究機関及び企業の研究開発部門が期待される。産業技術総合研究所では、「ファブシステム研究会」を、産業技術総合研究所九州センターでは「ミニマル 3DIC ファブ開発研究会」を立ち上げ、装置の技術開発やユーザーのニーズの発掘等を進めており、ミニマルファブ仕様の前工程~後工程の一連の装置の開発が進められているからであり、これらのラインで製作されたデバイスは必ず良品/不良品の検査装置が必要となるためである。まずはこの、ミニマルファブラインへの検査装置の組込みを検討している。また、一部企業においてもミニマルファブラインの構築が計画されており、今後は各研究会との連携を図りながらニーズの聞き取り、装置の開発、及び販売活動を推進していく予定である。